Le microprocesseur et son environnement (hardware)

SOMMAIRE

SYSTEME A BASE MICROPROCESSEUR

1 – INTRODUCTION.

2 – STRUCTURE DE BASE D’UN MICRO ORDINATEUR.

3 – QU’EST-CE QU’UNE INTERFACE ?

3.1 Interfaçage en entrée

3.2 Interfaçage en sortie

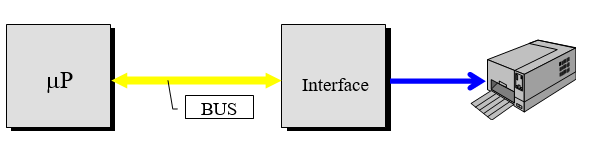

4 – Synoptique de base d’un système à micro-processeur.

5 – QU’EST-CE QU’UN MICRO-PROCESSEUR ?

5.1 Notion de mémoire.

5.2 Structure d’un microprocesseur.

6 – EXECUTION D’UNE INSTRUCTION.

7 – NOTION DE PROGRAMME.

8 – L’ENVIRONNEMENT DU MICROPROCESSEUR.

8.1 Exemple : architecture de base d’un PC XT.

8.2 Les bus.

8.3 Les mémoires.

8.4 Les ports d’entrée/sortie et circuits spécialisés.

8.5 Les circuits de décodage d’adresses.

8.6 Circuits d’horloge.

9 – TECHNIQUES D’INTERFACAGE.

9.1 Généralités

9.2 Le « Polling » ou mode programmé

9.3 Les interruptions

9.4 Accès direct à la mémoire (D.M.A)

LE MICROPROCESSEUR ET SON ENVIRONNEMENT (SOFTWARE)

1 – LES DIFFERENTES COUCHES DU LOGICIEL D’UN MICRO-ORDINATEUR.

1.1 Le Hardware (couche 1) :

1.2 Le Firmware (couche 2) :

1.3 Le Software (couche 3 – 4) :

2 – LE SYSTEME D’EXPLOITATION.

2.1 Les systèmes mono-tâches :

2.2 Les systèmes multi-tâches :

2.3 Les systèmes multi-utilisateurs :

3 – LES LANGAGES DE PROGRAMMATION.

3.1 Qu’est qu’un programme ?

3.2 Qu’est-ce qu’un langage de programmation ?

3.3 Interpréteurs et compilateurs

3.4 Les langages existants.

4 – Organisation mémoire d’un PC.

4.1 Organisation des 384 Ko supérieurs de la memory map.

4.2 Organisation des 640 Koctets de la RAM.

SYSTEME A BASE MICROPROCESSEUR

1 – INTRODUCTION.

Les premiers automatismes séquentiels (1937-1944) contenaient dans leur propre câblage l’organisation du déroulement des « tâches » à accomplir : le programme de la suite des opérations à effectuer, l’horloge n’imposant que le rythme de ces opérations.

Il en résultait deux inconvénients :

- * Le câblage était très complexe.

- * L’organisation du déroulement des opérations était figée.

Les premiers calculateurs (1945-1946) utilisaient cette méthode appelée « logique séquentielle câblée ».

A partir de 1946 le problème a été complètement repensé, l’organisation du déroulement (le programme) ne devait plus être câblée mais contenue sous forme d’instructions dans des bascules-mémoires, effaçables et réinscriptibles à volonté, cette nouvelle technique s’appelle « logique séquentielle programmée » elle a donnée naissance aux ordinateurs (1955) puis dans les années 70 est apparu le micro-processeur.

2 – STRUCTURE DE BASE D’UN MICRO ORDINATEUR.

Un ordinateur comprend au moins :

- – une unité centrale de traitement : UCT ou CPU (microprocesseur, P),

- – des mémoires internes stockant :

-

- * le programme,

- * les données sur lesquelles il travaille,

- – des circuits d’interface appelés ports ou circuits d’entrées-sorties.

Le tout est relié par un « bus« .

Le microprocesseur, les mémoires internes, etc… sont des circuits intégrés électroniques.

Il ne traite que le binaire.

Le microprocesseur ne peut traiter à la fois qu’un mot[1], constitué, selon les microprocesseurs de 8, 16, 32 bits.

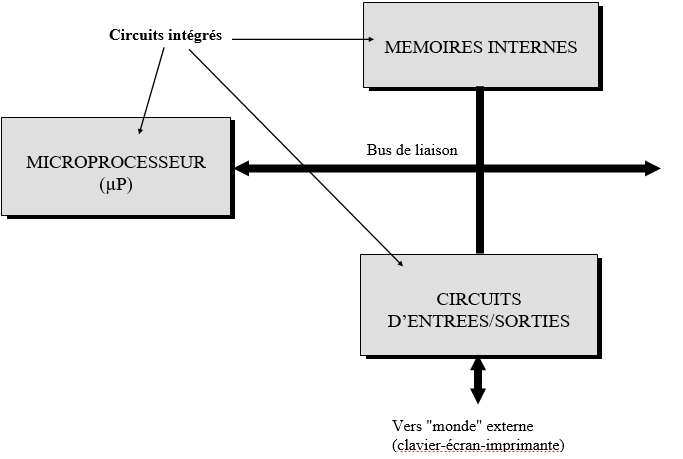

3 – QU’EST-CE QU’UNE INTERFACE ?

Dans un système à microprocesseur, l’interface (circuit intégré) va assurer la liaison entre l’unité centrale, via le bus interne du micro-ordinateur et l’environnement (périphérique).

3.1 Interfaçage en entrée

Les informations d’entrée proviennent :

- – soit de périphériques,

- – soit de la conversion de grandeurs physiques,

- – soit d’autres systèmes informatiques.

Les périphériques d’entrée :

- – le clavier,

- – le lecteur de ruban papier,

- – le lecteur de bande magnétique,

- – le lecteur de disque magnétique (dur ou souple),

- – le lecteur de cassette magnétique,

- – le lecteur optique (codes à barres, cartes perforées),

- – les convertisseurs (C.A.N. analogique numérique),

- – la souris.

3.2 Interfaçage en sortie

Les informations de sortie seront :

- – transmises vers des périphériques automatiques,

- – converties en des grandeurs physiques ou des commandes,

- – mises en forme pour être transmises via des réseaux de transmission vers d’autres ordinateurs.

Les périphériques de sortie :

- – affichage simples à diodes électroluminescentes,

- – affichage sur écran de visualisation (CRT),

- – imprimantes,

- – mémoires de masse,

- – perforateur de ruban,

- – programmeur de PROM,

- – convertisseur (CNA – numérique analogiques),

- – modem, fax.

4 – Synoptique de base d’un système à micro-processeur.

Tout ceci constitue le matériel (HARDWARE).

Comme on peut s’en douter, ce matériel, livré à lui-même, est totalement inutilisable. Il faut « l’animer » par un PROGRAMME: le logiciel (SOFTWARE). Ce logiciel s’installe en ROM et/ou en RAM.

Voir en annexe page 44, le synoptique de base d’un PC.

5 – QU’EST-CE QU’UN MICRO-PROCESSEUR ?

C’est un circuit intégré à très grande échelle (VLSI) capable d’exécuter automatiquement des instructions (opérations élémentaires) qu’il ira chercher dans la mémoire du micro-ordinateur.

C’est à partir du jeu d’instructions du microprocesseur que le programmeur ou le compilateur doit écrire le programme en mémoire.

5.1 Notion de mémoire.

Toutes les informations qu’utilise le microprocesseur sont stockées dans des mémoires, en particulier le programme, le fonctionnement du microprocesseur est entièrement conditionné par le contenu de celles-ci.

Ces mémoires contiennent deux types d’informations : les programmes et les données nécessaires pour la réalisation d’une tâche précise.

Les données ou OPERANDES proviennent, le plus souvent, d’un calcul effectué par le microprocesseur ou d’un périphérique d’entrée, (clavier, disque, …) via une interface. Elles sont stockées dans des mémoires qui peuvent être lues et écrites appelées RAM (Random Acces Memory).

On distingue deux types de programmes :

- – les programmes figés qui sont placés, de façon définitive, dans des mémoires qui ne pourront qu’être lues par le microprocesseur. Ce sont les ROM (Read Only Memory) appelées MEMOIRES MORTES. Tous systèmes à au moins ce type de programmes indispensables pour rendre utilisable le hardware (c’est ce que l’on appelle BIOS dans un PC).

- – Les micro-ordinateurs peuvent exécuter des tâches diverses, (traitement de texte, gestion de paye, etc. ); ces programmes sont stockés sur des supports magnétiques (disquettes, disque) appelés MEMOIRES AUXILIAIRES ou MEMOIRES DE MASSE.

Ces programmes ne sont chargés en mémoire que lors de leur exécution. Ils sont transférés dans des MEMOIRES VIVES ou RAM (Random Acces Memory).

5.2 Structure d’un microprocesseur.

Les microprocesseurs se distinguent suivant les caractéristiques suivantes :

Les registres :

Ce sont des mémoires intégrées au microprocesseur. Tous les calculs et autres traitements de données doivent passer par des registres. Un microprocesseur ne peut opérer directement sur la mémoire centrale. Chaque opération consiste donc à un premier échange de la mémoire centrale vers les registres du processeur (LOAD), au traitement des données chargées, puis à un autre échange des registres vers la mémoire (STORE). Plus les registres sont grands, moins le nombre d’échanges est important, donc plus la machine est rapide.

Le bus des données :

C’est l’organe physique d’échange des données entre le processeur et la mémoire centrale. Plus le bus des données est « large » (Nbre de fils), plus on peut échanger des données en même temps, moins le nombre d’échanges est important, donc plus la machine est rapide.

Le bus des adresses :

C’est grâce à ces fils que le P localise (adresse) des informations dans la mémoire.

La capacité maximum de mémoire que peut gérer un micro-ordinateur dépend de la taille de ce bus (2N – N étant le Nbre de fils).

La fréquence :

Celle-ci se mesure en MHz ( MegaHertz ). C’est le nombre de cycles machine (en millions par seconde) que peut effectuer un microprocesseur. Pour exécuter une instruction un processeur utilise 1 ou plusieurs cycles machines selon la complexité de celle-ci. L’exécution d’une instruction nécessite d’un processeur à l’autre un nombre de cycle différent.

Plus la fréquence est élevée, plus la machine est rapide.

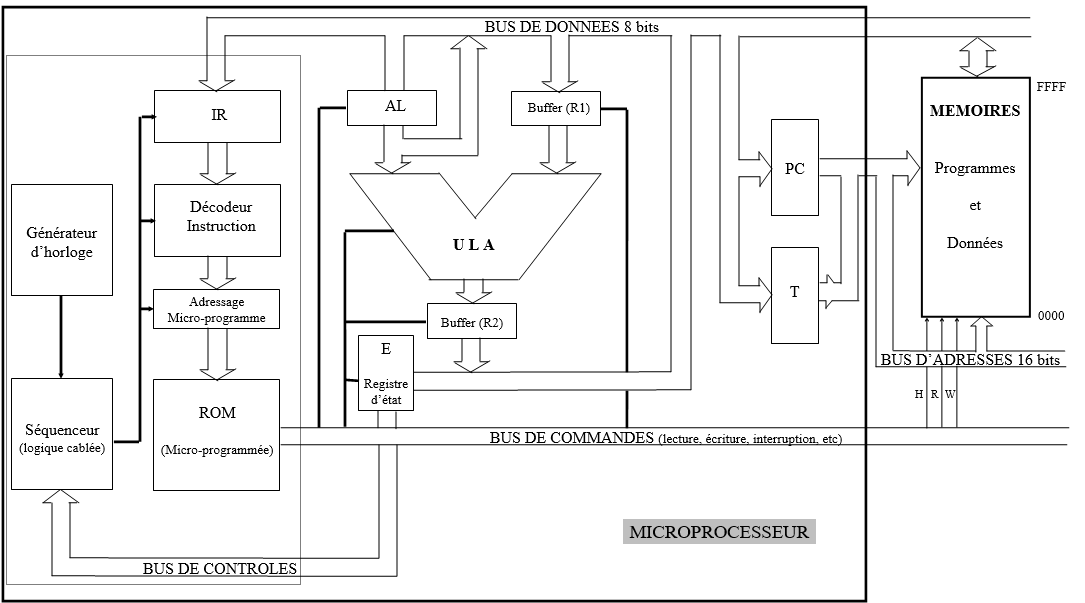

Soit le schéma 1 fourni en annexe qui représente un microprocesseur théorique et simplifié. On trouve :

Pour les échange entre les registres internes et l’extérieur :

- – Un réseau de fils parallèles associés par 8, 16, 32 ou 64 nommé BUS DE DONNEES destiné à véhiculer, entre autre, les informations et les données reçues et envoyées par l’UAL et les REGISTRES.

- – Un réseau de fils parallèles associés par 16,24 ou 32, nommé BUS D’ADRESSES qui permet d’adresser 2n cases mémoires, par exemple si n = 16 on aura 64 kilo-octets de mémoire accessible.

- – Un BUS DE COMMANDE qui sera détaillé plus tard.

- – Des bornes d’alimentation.

A l’intérieur on trouve :

- – Un sous-ensemble appelé UNITE ARITHMETIQUE ET LOGIQUE (UAL) ou ALU (Arithmetic Logic Unit), constitué par un très grand nombre de fonctions logiques combinatoires (ET, OU, NON, OU exclusif, etc…) regroupées chacune par 8, 16 voir 32.

- – Des REGISTRES de 8, 16 ou 32 bits qui permettent pour certains de conserver pendant de courts instants les données logiques traitées par l’ULA, pour d’autres des adresses. Certains de ces registres sont « accessibles » par le programmeur tandis que d’autres sont utilisés de façon transparente par le microprocesseur.

Dans l’exemple on a en particulier le registre AL appelé ACCUMULATEUR, ce registre contient un des opérandes (avant l’opération) et le résultat (après l’opération).

Le registre PC (Program Counter), qui fonctionne un peu comme un compteur, contient en permanence l’adresse de la prochaine case mémoire que le microprocesseur ira lire ou écrire.

- – La partie à l’intérieur des pointillés est constitué par un assemblage particulièrement complexe de circuits combinatoires et séquentiels nommé UNITE DE COMMANDE.

Ce sous-ensemble, dont le fonctionnement est complètement transparent pour le programmeur, ordonnance l’exécution des INSTRUCTIONS du PROGRAMME, coordonne tous les TRANSFERTS D’INFORMATIONS à l’intérieur comme à l’extérieur du microprocesseur pour ce faire l’unité de commande génère et gère le BUS DE COMMANDE.

En résumé… Un µP de base comprend…

|

L’UAL ou ALU |

|

|

Les REGISTRES |

|

|

Les BUS |

|

|

L’UNITE DE COMMANDE |

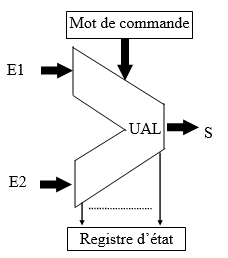

5.2.1 L’UAL (ou ALU) Unité Arithmétique et Logique.

Deux données binaires E1 et E2 formées

Deux données binaires E1 et E2 formées

chacune d’un OCTET (sur 8 fils) ou d’un

double-octet (16) sont combinées dans

l’UAL et donnent en Sortie S un nouvel

octet (ou double octet) disponible pour

la suite des opérations prévues par le programme.

Les opérations que peut réaliser un processeur sont très élémentaires et sont exécutées dans l’ALU (sur 8, 16, 32 bits) :

- * La Complémentation (le NON).

- * Le ET logique.

- * Le OU logique.

- * Le OU exclusif.

mais aussi, par combinaison de ces fonctions de base :

- * L’ADDITION.

- * La SOUSTRACTION.

- * La MULTIPLICATION.

- * La DIVISION.

- * La COMPARAISON.

et avec l’aide de Registres voisins…

- * Le DECALAGE A DROITE.

- * Le DECALAGE A GAUCHE.

- * L’INCREMENTATION (on ajoute 1).

- * La DECREMENTATION (on retranche 1) et d’autres…

Remarque: Les microprocesseurs de dernière génération peuvent travailler sur 32 bits (par exemple 80386,80486). Cependant sous MSDOS ils se comportent comme un 8086 (16 bits)

C’est le MOT DE COMMANDE, fourni par l’UNITE DE COMMANDE qui donne l’ordre à l’ALU d’effectuer l’une ou l’autre des opérations citées ci-dessus.

L’ALU réalise une autre fonction qui consiste à mettre à jour le REGISTRE D’ETAT qui contient des indicateurs (bits) qui sont positionnés en fonction du résultat de l’opération précédente. Citons par exemple :

– Le bit de retenue ou CARRY : Ce bit est positionné si une addition à produit une retenue, le programmeur pourra tester ce bit afin d’en tenir compte pour la suite des opérations.

– L’indicateur de ZERO : Ce bit signale si le résultat d’un opération est nulle, le programmeur l’utilisera pour les opérations de comparaison.

5.2.2 L’unité de commande (transparente pour l’utilisateur).

Elle est constituée par :

– Le registre d’instruction IR.

– Le décodeur d’instructions.

– La mémoire contenant le microprogramme.

– Le séquenceur.

– Le générateur d’horloge.

Le registre IR contient le code binaire de l’instruction que le µP va effectuer; cette instruction est décodée grâce au Décodeur d’instructions qui fourni l’adresse de début d’un petit programme écrit dans une mémoire ROM. Cette ROM contient autant de micro programmes qu’il y a d’instructions.

C’est le Séquenceur qui au rythme de l’horloge adresse cette ROM afin d’exécuter le micro programme.

Chaque instruction de ce micro programme fait apparaître, au rythme de l’horloge des « 1 » et « 0 » sur un ensemble de fils nommé le bus de commandes; l’ensemble des modules internes est connecté à ce bus.

Il permet, par exemple, d’indiquer à l’ULA l’opération à réaliser sous la forme du mot de commande.

La taille du micro programme dépend de la complexité de l’instruction; si l’instruction est simple il suffit de quelques cases mémoires. Une instruction peut donc s’effectuer en quelques périodes d’horloge ou en quelques dizaines de périodes selon la longueur du micro programme.

Un tel système ne peut fonctionner que s’il y a un contrôle de l’exécution; le registre d’état E vient en retour au niveau du séquenceur. Ceci permet des tests, des sauts conditionnels (voir plus loin pour plus d’informations).

6 – EXECUTION D’UNE INSTRUCTION.

Chaque instruction est exécutée par le µP selon une séquence de trois phases:

1 Recherche « FETCH »

2 Décode et analyser « DECODE »

3 Exécution « EXECUTE »

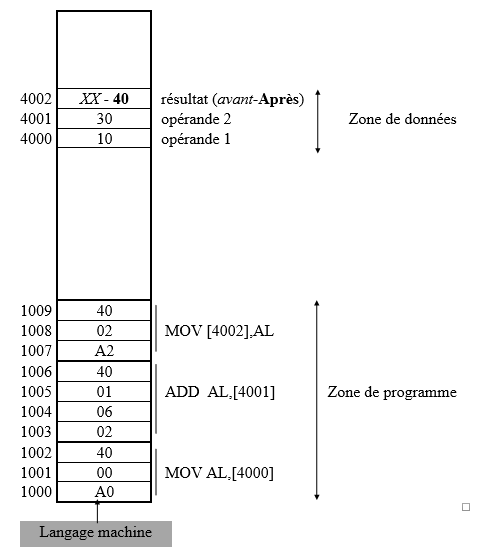

Nous allons illustrer cela par l’exécution d’un petit programme de trois instructions écrit dans la RAM à partir de l’adresse 1000 qui additionne le contenu de l’adresse 4000 avec le contenu de l’adresse 4001 puis enregistre le résultat en 4002.

Ces instructions nécessitent chacune au moins 3 octets :

– Le premier est le code décrivant l’instruction[2], il sera placé dans le registre IR lors du FETCH puis décodé par le décodeur d’instruction lors du DECODE.

– Le deuxième et le troisième sont nécessaires pour contenir l’opérande ou l’adresse de l’opérande.

Chaque microprocesseur possède un jeu d’instructions que l’on peut utiliser sous la forme de MNEMONIQUES, les micros de la famille x86 de chez Intel proposent pour ces opérations :

– MOV (transfert) pour la première et troisième instruction;

– ADD (addition) pour la deuxième instruction;

Le programme peut s’écrire de la façon suivante dans un langage que l’on nomme l’ASSEMBLEUR :

MOV AL,[4000] ; Transférer le contenu de l’adresse 4000 dans le registre AL (accumulateur)

ADD AL,[4001] ; Addition du contenu de AL avec le contenu de l’adresse 4001, résultat dans AL

MOV [4002],AL ; Transfert du contenu de AL (résultat) dans l’adresse 4002.

Le contenu de la mémoire après exécution du programme sera :

Le rôle d’un assembleur, comme le montre la figure ci-dessus est de traduire les mnémoniques en mot binaire, seul langage compréhensible par le P, par exemple MOV AL,[4000] est traduit par A0 (code de l’instruction) et 0040 adresse 4000.

On peut remarquer que certaines instructions nécessitent plusieurs codes machines par exemple ADD AL,[4001] est codée par 02, 06 pour l’instruction et 0140 pour l’adresse.

Nous allons suivre sur le schéma de l’annexe 1, le déroulement séquentiel de ce programme.

Hypothèse de départ le registre PC contient la valeur 1000 qui correspond au début du programme.

– Première instruction :

L’unité de commande donne l’ordre de déposer le contenu du registre PC sur le bus d’adresses et positionne la mémoire en lecture par l’intermédiaire d’une ligne du bus de commande (READ), l’octet A0 contenu de la case 1000, est donc présent sur le bus de données et est transféré dans le registre IR. Opération FETCH.

L’octet A0, code de l’instruction MOV AL,[xxxx], est décodé par le Décodeur d’instructions qui lance le micro programme correspondant. Opération DECODE.

La première opération de ce micro programme consiste à aller chercher dans la RAM l’adresse de l’opérande pour ensuite charger dans AL le contenu de celle-ci soit :

* Le compteur PC est incrémenté et « pointe » l’adresse 1001;

* le mot 0040 (contenu de 1001 et 1002) est mis dans le registre T, qui contient alors l’adresse de la première opérande soit 4000.

* le compteur PC est incrémenté et « pointe » l’adresse 1003 mais ses sorties sont mises par l’unité de commande en haute impédance (coupées du bus d’adresses). Par contre, les sorties du registre T sont validées ainsi que la ligne Read du bus de commande, de ce fait, l’adresse 4000 est présente sur le bus d’adresses et son contenu (10) est présent sur le bus de données et est recopié dans le registre AL. Opération EXECUTE

* Pour terminer le cycle les sorties du registre T sont remises en haute impédance et les sorties du registre PC sont validées.

Fin de la première instruction.

– Deuxième instruction :

Le contenu du PC (1003) est déposé sur le bus d’adresse pointant ainsi la deuxième instruction.

Le mot 02, est placé dans IR et indique qu’il s’agit d’une instruction codée sur deux octets.

* Le compteur PC est incrémenté et « pointe » l’adresse 1004;

* Le contenu de 1004 (06) est placé dans le registre IR.

Fin de l’opération de FETCH.

Après décodage de l’instruction un micro programme est exécuté au coeur du µP qui consiste comme pour l’instruction N°1 à récupérer l’adresse du deuxième opérande (4001) puis à transférer le contenu de 4001 (30) dans le registre R1 (invisible pour le programmeur).

L’UAL reçoit par l’intermédiaire du mot de commande, issu du micro programme, l’ordre d’effectuer l’addition de AL avec R1 et de mettre le résultat, soit 40, dans R2, (lui aussi, invisible pour le programmeur). Il est à noter que le registre d’état est modifié lors de cette opération en particulier le flag CARRY est mis à 0, pas de retenue.

Les sorties de R2 sont validées et le contenu de celui-ci est recopié dans AL.

Le PC contient à cet instant la valeur 1007 qui est l’adresse de la prochaine instruction.

Fin de la deuxième instruction.

– Troisième instruction.

Cette instruction se déroule de façon analogue à la première à la différence près que c’est le contenu de AL qui est copié en mémoire et non pas le contraire.

7 – NOTION DE PROGRAMME.

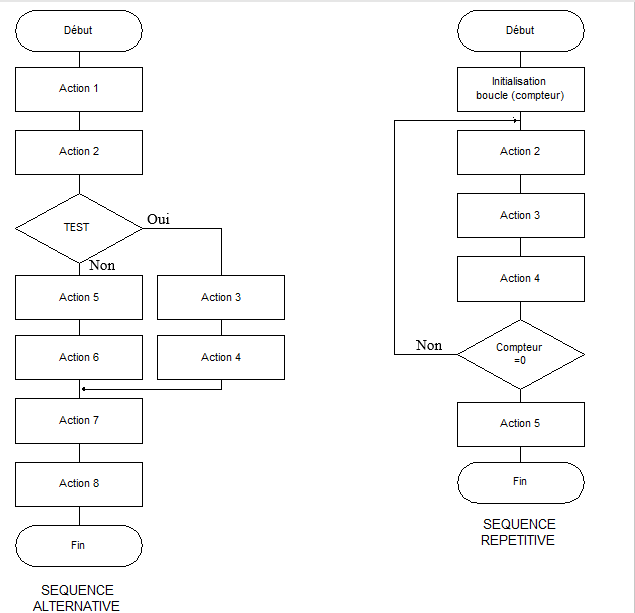

Le programme précédent est une suite d’instructions linéaires, en réalité la plupart des programmes nécessitent des tests, des comparaisons, comme l’illustre le programme d’horloge numérique page 36, ce qui conduit à écrire des programmes dont la suite des instructions n’est plus linéaire. Avant d’écrire les instructions de tels programmes il est indispensable d’en décrire le déroulement soit à l’aide d’un pseudo langage voir en annexe page 36 ou d’un organigramme page 37.

Dans un organigramme :

– Chaque action est décrite dans un rectangle (faire un OU entre AL et le contenu d’une case mémoire par exemple).

– Chaque comparaison ou test est décrit dans un losange

(par exemple AL > 15).

Dans les exemples ci-dessus, on trouve :

– Une structure alternative (à gauche) dans laquelle un test permet le choix entre deux branches de l’organigramme.

– Une structure répétitive ou boucle (à droite) dans laquelle les actions 2, 3 et 4 sont exécutées plusieurs fois. Cette séquence possède un compteur (registre interne du processeur) qui doit être initialisé avant la boucle et décrémenté puis testé lors de chaque passage, lorsque le compteur est égal à 0, la séquence 5 est exécutée.

Dans des cas concrets on trouve une combinaison de ces différentes structures.

Suite à un test ou une comparaison le microprocesseur en fonction de la « réponse » exécute soit l’instruction suivante soit une instruction située plus loin en mémoire, c’est le rôle des instructions de saut.

Prenons par exemple l’organigramme de droite, le programme s’exécute ainsi :

– Action 1, action 2, TEST (on suppose vrai), action 3, action 4 et ici il faut sauter les instructions correspondants aux actions 5 et 6, pour aller exécuter l’action 7. Dans ce cas on dit que le saut est inconditionnel, car après l’action 4 on exécute toujours l’action 7.

– Supposons maintenant que le TEST soit faux; le processeur doit sauter les instructions correspondantes aux actions 3 et 4 pour aller exécuter les actions 5 et 6. Dans ce cas on dit que le saut est conditionnel.

Tous les microprocesseurs possèdent des instructions de test et de comparaison ainsi que des instructions de saut.

C’est le registre d’état, qui est utilisé pour les sauts conditionnels. Ce registre, comme décrit dans les chapitres précédents, contient des indicateurs qui sont positionnés par le résultat de l’opération précédente.

Exemple :

Il existe un indicateur, nommé Z, qui est positionné à 1 lorsque le résultat de l’opération précédente est nul et à 0 dans le cas contraire. Z permet ainsi d’exécuter des sauts conditionnels de type saut si compteur # de zéro (JNZ ou JNE) ou au contraire saut si le compteur est égal à zéro (JZ ou JE).

L’association de Z et de C (Carry) permet de réaliser des sauts conditionnels, suite à une comparaison, de type : saut si supérieur (JA), saut si inférieur (JB), saut si supérieur ou égal (JAE), saut si inférieur ou égal (JBE).

Les manipulations vous permettrons de mettre en œuvre ce type d’instructions.

8 – L’ENVIRONNEMENT DU MICROPROCESSEUR.

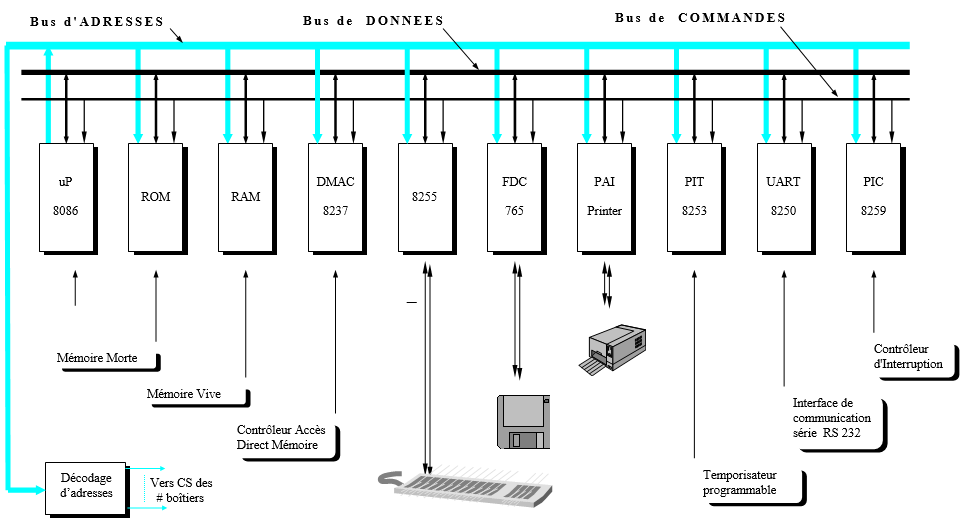

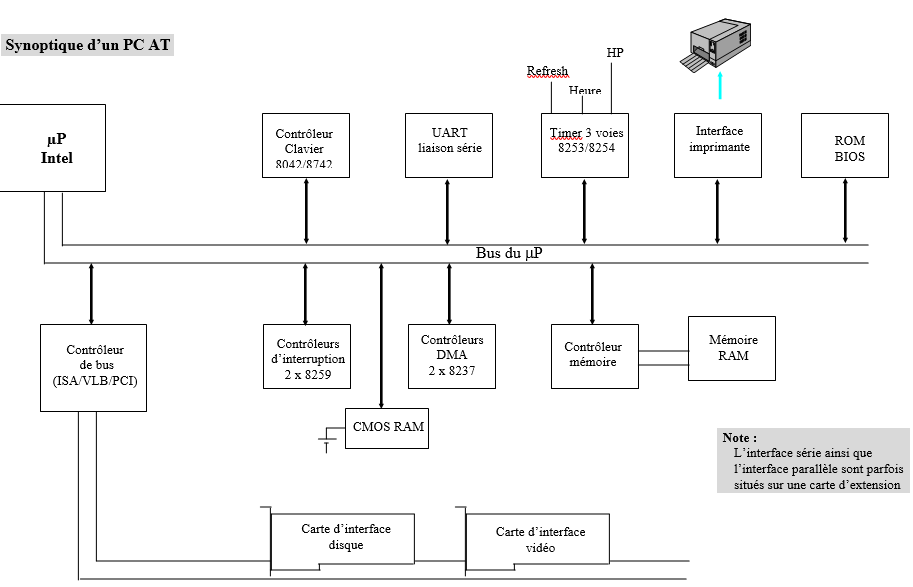

8.1 Exemple : architecture de base d’un PC XT.

Tout ceci constitue le matériel (HARDWARE).

8.2 Les bus.

Un bus est constitué de n lignes en parallèles qui permettent de transmettre des informations ou des signaux, groupés par fonction.

Un micro-processeur gère trois bus :

– Le bus de données qui véhicule les données échangées entre les différents modules. Le bus de données est bi-directionnel et possède 8, 16, 32 ou 64 lignes en parallèles selon que le micro-processeur est à 8, 16, 32 ou 64 bits.

Si le BUS de DONNEES a 8 fils, ils se numérotent de D0 à D 7.

a 16 fils, ils se numérotent de D0 à D15.

a 32 fils, ils se numérotent de D0 à D31.

ROM

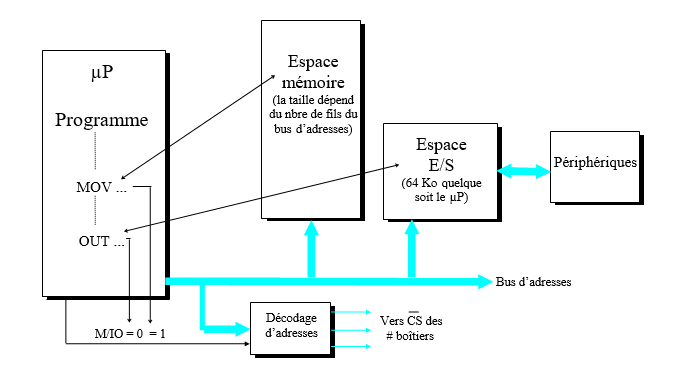

– Le bus d’adresses permet au micro-processeur de sélectionner la source ou la destination des informations transitant sur le bus de données. Il véhicule des adresses; il est composé de 16, 20, 24 ou 32 fils.

Dans le cas des processeurs Intel (voir figure ci-dessous) l’espace mémoire, constitué des différentes RAM et ROM du système, est distinct de l’espace E/S, constitué par tous les circuits d’interface (E/S), la sélection est réalisée en fonction des instructions du programme qui selon le cas positionne à 0 ou à 1 la ligne M/IO du bus de commande.

Si le BUS d’ADRESSES a 24 fils, (80286 ou 80386 SX), ils se numérotent de A0 à A23. Il peut alors ADRESSER: 167777216 « lieux » soit 16 Moctets.

Si le BUS d’ADRESSES a 32 fils, (80386 DX, 80486 et Pentium), ils se numérotent de A0 à A31. Il peut alors ADRESSER: 4294960000 « lieux » soit 4 Goctets.

– Le bus de commandes assure la synchronisation des opérations du système.

Exemples :

* les horloges

* la ligne d’écriture ou de lecture

* les interruptions

* Reset

* Contrôle DMA

* Mise en attente (Ready).

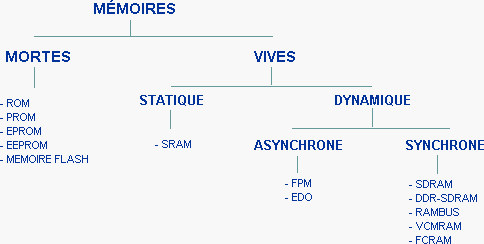

8.3 Les mémoires.

Le µP travaille « sous les ordres » d’un PROGRAMME. Il est donc indispensable que celui-ci soit « installé » à l’avance dans des MEMOIRES soit en RAM (lecture/écriture, volatile) ou soit en ROM (lecture seule, permanent).

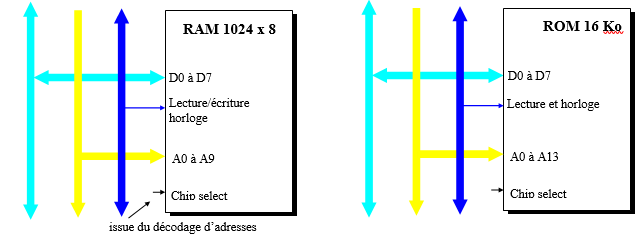

Un µP est donc associé à de la ROM et de la RAM. Il y accède par l’intermédiaire du Bus d’Adresses qui permet de LOCALISER une information (1 octet) et par le Bus de Données où « voyage » l’octet recueilli (en ROM) ou à écrire ou à lire (en RAM). Il existe différents famille de mémoire, la figure ci-dessous résume l’état actuel.

Le fonctionnement de ces différentes technologies sera détaillé lors du cours intégration

8.3.1 La mémoire vive.

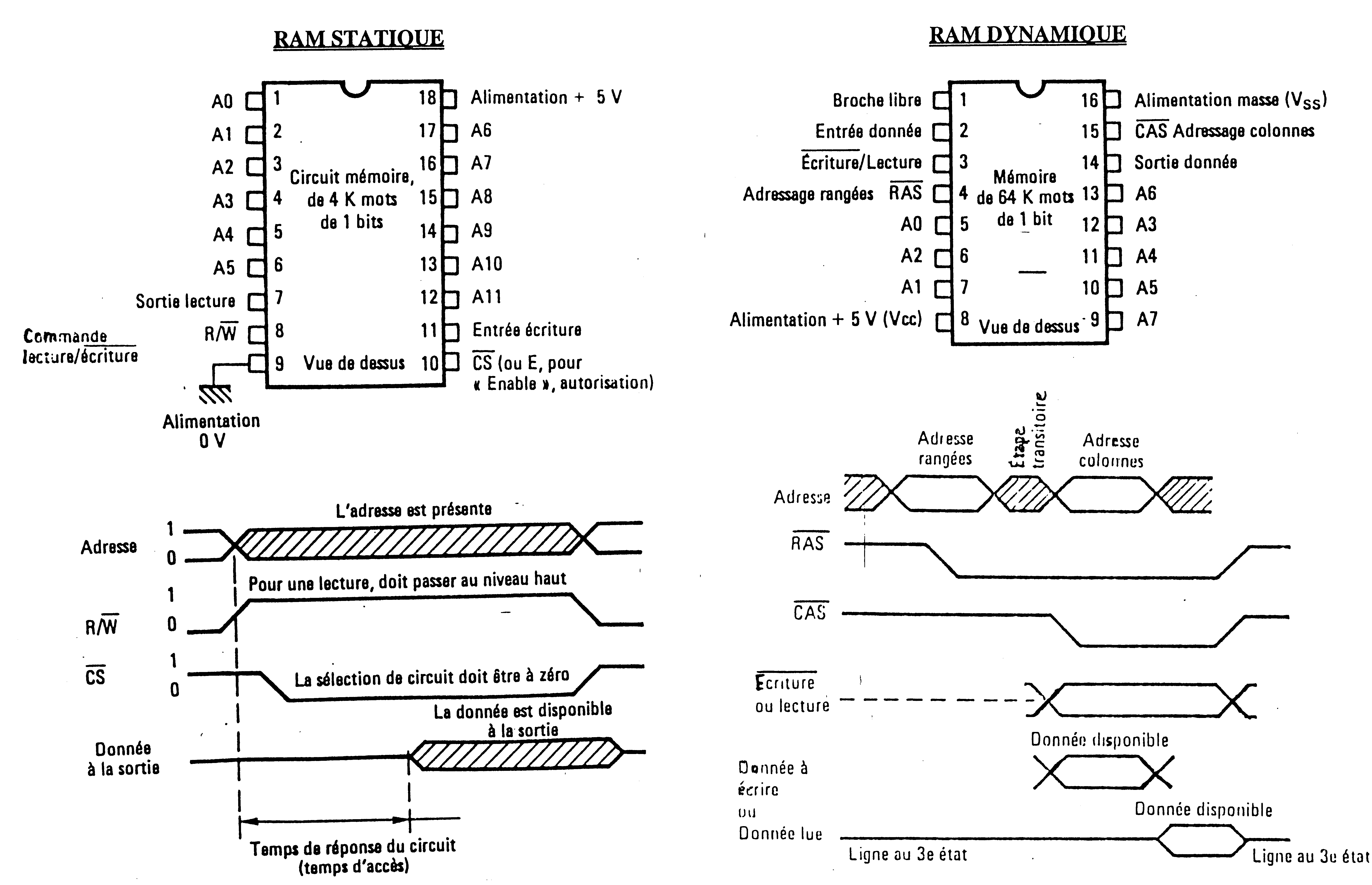

Il existe deux types de RAM : les RAM statiques et les RAM dynamiques:

Dans une RAM statique, il faut 4 transistors pour mémoriser un bit.

Les RAM statiques permettent un accès très rapide en lecture/écriture mais elle ne permettent pas une intégration aussi importante que les RAM dynamiques. Elles sont aussi beaucoup plus chères. Elles sont principalement utilisées pour constituer la mémoire cache des cartes mères.

Dans une RAM dynamique, il ne faut qu’un seul transistor (et un « condensateur ») pour mémoriser un bit.

Les RAM dynamiques permettent une très forte intégration. Cependant elles nécessitent d’être lues cycliquement[3] pour conserver leurs informations (opération appelée rafraîchissement). Elles sont plus lentes en accès lecture/écriture mais bien meilleur marché que les RAM statiques.

Différentes technologies se sont succédées dont la finalité est de permettre un accès de plus en plus rapide :

Les mémoires asynchrones (les plus ancienne) :

Citons la FPM[4] présentes sur les cartes mères à base de 386 et 486 qui a été remplacée par l’EDO[5] qui a fait son apparition sur la dernière génération de carte mère à base de 486 et s’est généralisée sur les cartes mères à base de Pentium et AMD K6. Ces 2 types de RAM on comme principal inconvénient de ne pas pouvoir travailler à la même vitesse que les processeurs actuels, pour remédier à ce problème une nouvelle technologie a été mise au point :

Les mémoires synchrones :

Citons la SDRAM[6] qui équipent les cartes mères pour Pentium II et III et AMD Atlon. Elle permet de fonctionner, selon les versions à 66, 100 et pour les plus récentes 133 Mhz.

Une nouvelle technologie la DRDRAM[7] fait son apparition sur les cartes mères construites autour du chipset d’Intel l’I820 et processeur Pentium III, elle a pour avantage majeur son temps d’accès très rapide mais est encore trop chère.

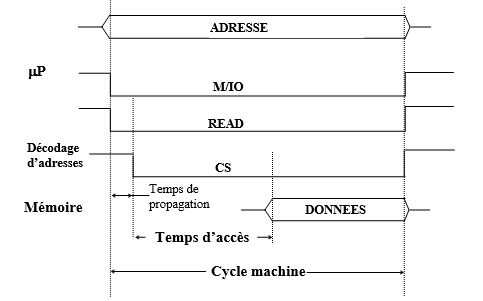

Un des problèmes à résoudre par les concepteurs de carte à base de processeur c’est d’adapter la vitesse de travail du processeur au temps d’accès de la mémoire. Prenons comme exemple un processeur dont la fréquence du bus externe est de 66 MHZ travaillant avec de la mémoire dont le temps d’accès est de 70 ns

Une fréquence de 66 Mhz correspond une période de 15 ns (inverse de la fréquence). C’est pendant ce laps de temps que la mémoire sollicitée doit répondre à l’ordre reçu. Si son temps d’accès est de 70 ns, c’est matériellement impossible. Le principe utilisé dans ce cas est décrit page suivante :

Pour que la mémoire ait le temps de répondre à la sollicitation (lecture ou écriture), le processeur sera mis en attente pendant cinq périodes d’horloge, soit 15*5 = 75 ns, par une broche du bus de commande appelée Ready.

Ces périodes d’horloge supplémentaires sont appelées des « temps d’attente », ou des « Wait States ».

8.3.2 La mémoire morte.

Ces mémoires ne sont accessibles qu’en lecture et conservent leurs données de façon permanente; elles sont désignées par le terme générique ROM ( Read Only Memory ).

En fait, le sigle ROM désigne toute une famille de produit :

ROM Mémoire programmée lors de leur fabrication. Il n’est plus possible de modifier leur contenu.

PROM Mémoire morte programmable par l’utilisateur. Le fabricant de micros y stockera le BIOS de ses machines. Son contenu ne peut plus être modifié.

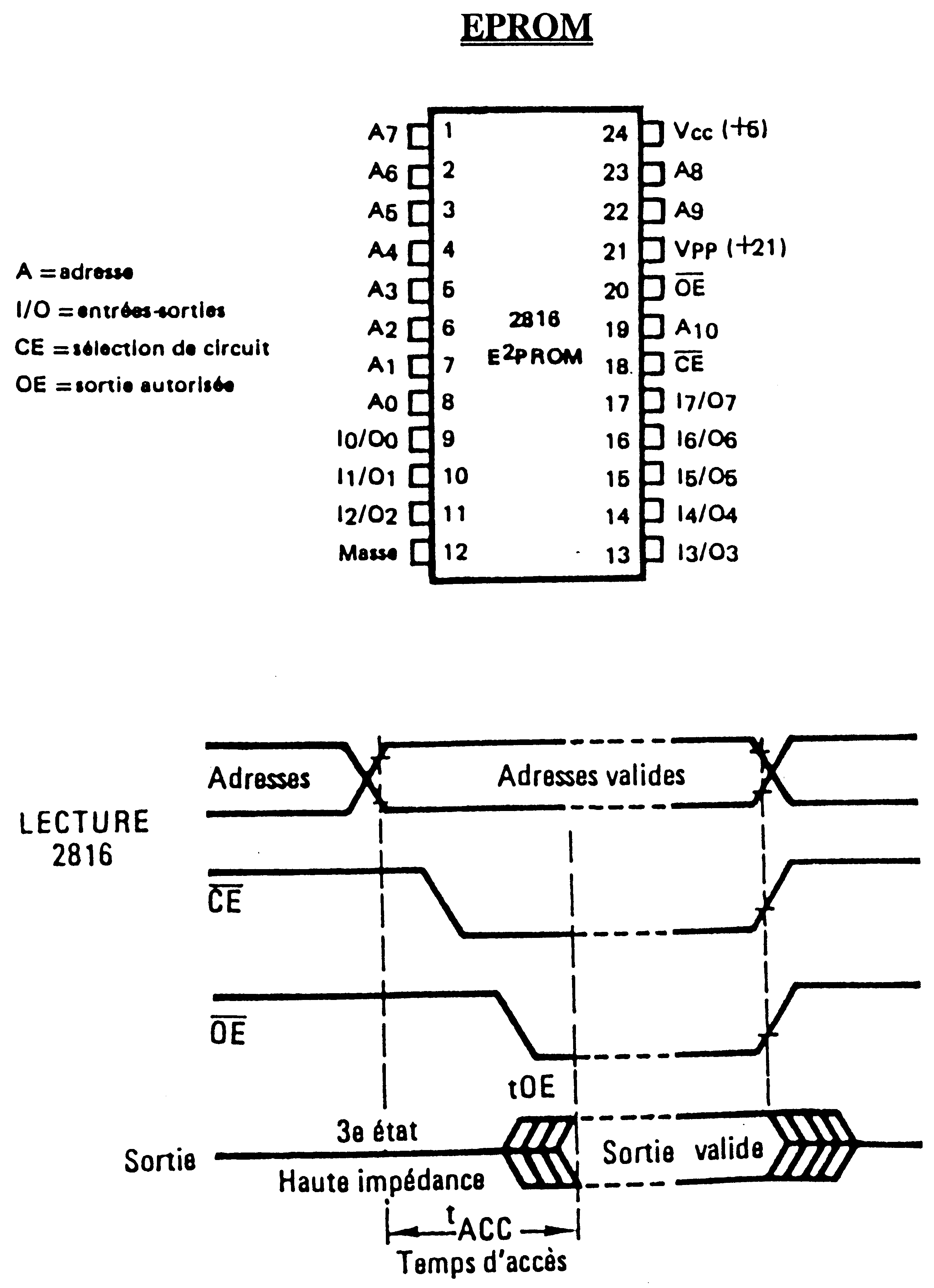

EPROM /REPROM La programmation s’effectue électriquement mais il est possible d’effacer le contenu par exposition aux ultraviolets et de reprogrammer le circuit.

EEPROM Programmable et électriquement effaçable. L’effacement de ce type de mémoire se fait par l’application d’une tension sur une des broches du circuit.

Mémoire Flash Elle s’apparente aux EEPROM mais de technologie plus récente. La quasi totalité des cartes mères actuelles ont leur BIOS sauvegardé dans ce type de mémoire ce qui permet la mise à jour éventuelle du BIOS par l’utilisateur, à partir d’une disquette.

8.3.3 Caractéristiques.

– La capacité en nombre de bits.

Exemple : 16 K bits 256 K bits 1 M bits

– Son organisation.

Exemple : mot de 1 bit, de 4 bits, de 8 bits.

8.3.4 Méthode d’accès.

* Cycle de Lecture (voir timing ci-dessous)

Pour lire le contenu d’une case mémoire il faut :

– Que le micro-processeur génère une adresse et un signal de lecture (Read) ainsi que la ligne M/IO.

– Que le ou les boîtiers mémoires soient sélectionnés par l’intermédiaire de 1 (ou plusieurs) « chip select », issu du décodage d’adresses, dont le rôle est d’indiquer au boîtier que l’adresse présentée à ses bornes lui est destinée.

– Au bout d’un temps dit temps d’accès les données sont disponibles et déposées sur le bus de données par la mémoire, le micro-processeur peut ainsi les lire.

* Ecriture

Le processus est analogue à celui d’une lecture sauf que le microprocesseur doit positionner sa ligne d’écriture.

8.4 Les ports d’entrée/sortie et circuits spécialisés.

Le µP, associé à ses Mémoires ne servirait absolument à rien s’il ne pouvait COMMUNIQUER AVEC L’EXTERIEUR (de la Carte-Mère).

Il doit être capable de « piloter » :

Un Clavier.

Un écran cathodique (ou à Cristaux liquides).

Un système de disquettes ou de disque dur.

Une imprimante.

et, pourquoi pas…

Une table traçante.

Une machine-outil.

Pour cela il existe des circuits intégrés, appelés circuits d’interface, spécialisés pour la gestion des différents périphériques. Ces circuits contiennent des registres qui doivent être accessibles par le microprocesseur, il faut donc réserver certaines adresses pour ces registres que l’on appelle PORTS.

Grâce à ces « ports », le µP peut ENVOYER des OCTETS vers l’extérieur ou en RECEVOIR.

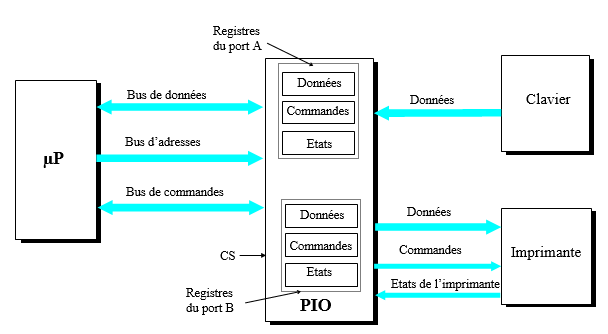

Les circuits d’interface permettent de « relier » le micro-processeur au « monde extérieur ». Ils permettent de « piloter » des périphériques d’entrées ou de sorties. Tous ces circuits sont programmables par le micro-processeur par l’intermédiaire de registres.

Les principaux circuits d’interface d’un PC[8] :

L’interface d’entrées-sorties parallèle (PPI ou PIO) :

PPI 8255 Programmable Peripheral Interface

Ce circuit a trois ports d’entrées-sorties de 8 bits chacun.

Dans un PC XT, ce circuit assure le lien entre l’unité centrale et des périphériques tels que le clavier ou le haut-parleur. Il sert également à accéder à certains interrupteurs de configuration situés sur la carte mère. Les échanges entre ce circuit et les périphériques se font sur un mode parallèle, c’est-à-dire que les différents bits nécessaires à une donnée sont présentés sur autant de fils de signaux logiques.

L’interface série (UART) :

UART 8250 Universal Asynchronous Receiver/Transmitter

Il contrôle l’interface RS 232C. Les paramètres de communication tels que la vitesse de transfert, la longueur des mots, les bits de stop et de parité peuvent être contrôlés par ce circuit LSI.

L’adaptateur d’imprimante (PAI) :

PAI printer Programmable Adaptator Interface

Il assure l’interface entre le bus de données du microprocesseur et le port parallèle du connecteur de l’imprimante.

Le Contrôleur de lecteur de disquettes (FDC) :

FDC 765 Floppy Disk Controller

Ce composant est soit situé sur la carte mère soit situé sur une carte d’extension. Il contrôle directement les fonctions du lecteur de disquettes, comme déplacer la tête de lecture/écriture sur la surface de la disquette, lire ou écrire des données sur la disquette.

Le timer programmable (PIT) :

PIT 8253 Programmable Interval Timer

Ce circuit peut être utilisé comme compteur ou comme chronomètre : il délivre sur chacun de ses canaux de sortie des impulsions à intervalles de temps fixés et constants; la fréquence de ces impulsions est programmable.

Chaque canal de sortie(3 dans le boîtier) est relié à un périphérique différent: ainsi, un canal pilote le haut-parleur, un autre le contrôleur d’interruptions (pour déclencher le rafraîchissement des RAM).

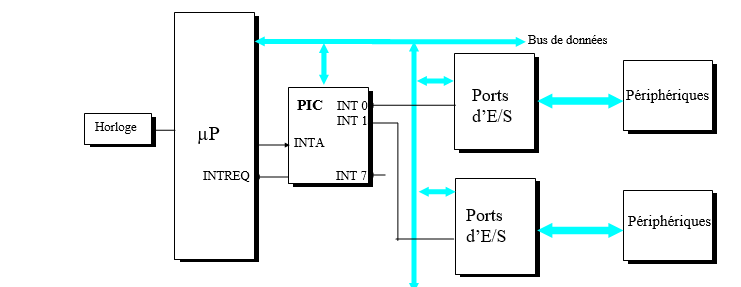

Le Contrôleur d’interruptions (PIC) :

PIC 8259 Programmable Interrupt Controller

Les différents composants du système disposent d’un mécanisme particulier pour attirer l’attention de l’unité centrale afin de lui faire effectuer une opération déterminée : il s’agit des interruptions.

Plusieurs interruptions pouvant survenir au même instant de différents composants, un circuit contrôleur d’interruptions établit des priorités entre ces interruptions et retransmet en premier lieu au microprocesseur la demande de priorité la plus élevée.

Un contrôleur d’interruptions peut traiter jusqu’à 8 demandes simultanées; les contrôleurs peuvent être associés en cascade pour gérer un nombre supérieur de demandes d’interruptions.

Un XT contient un circuit 8259, et peut traiter 8 demandes d’interruptions.

Un AT contient deux circuits 8259 et gère jusqu’à 15 demandes d’interruptions.

Le Contrôleur d’Accès Direct Mémoire (DMAC)

DMAC 8237 Direct Memory Access Controller

Le circuit DMA ( Direct Memory Access ) est capable d’écrire ou de lire des données directement en RAM sans passer par le processeur. Cette caractéristique est surtout intéressante pour 1’entrée/sortie de données issues de périphériques lents, tels qu’un lecteur de disquettes.

Ce circuit est également utilisé dans les PC XT pour le rafraîchissement des RAM dynamiques.

Note : La plupart de ces circuits sont intégrés sur les cartes mères actuelles sur un seul circuit du chipset.

Le Contrôleur d’écran :

Ce type de circuit, présent sur les cartes vidéo, permet de gérer l’affichage des données sur un écran.

Notes : Les circuits LSI ci-dessus sont connectés aux bus d’adresses, au bus de données et au bus de contrôle pour synchroniser leurs fonctions, et sont contrôlés directement ou indirectement par le CPU.

Les Coprocesseurs[9] :

Ces circuits sont spécialisés dans le traitement de données spécifiques. Ils travaillent en parallèle avec le processeur.

Exemple: coprocesseur arithmétique, le microprocesseur « sous-traite » à son coprocesseur les calculs à virgule flottante. C’est un circuit qui comme le microprocesseur est capable d’exécuter des instructions.

8.4.1 Architecture d’une interface.

Signaux circulant entre l’interface et le périphérique.

Quatre types de signaux peuvent circuler entre une interface programmable et un périphérique, la présence simultanée de ces quatre types de signaux étant d’ailleurs possible mais peu fréquente :

* des données transmises en principe par 8 fils parallèles ou en série cas de l’UART.

* des signaux de commande : ils sont déterminés par le constructeur pour s’adapter, tant au périphérique qu’à son mode d’exploitation.

* des signaux d’état transmettant des informations comme « périphérique prêt », « périphérique ou circuit externe ayant des données à transmettre ». Par exemple BUSY pour une imprimante

* des signaux de dialogue prévus dans le circuit interface sur des broches précises pour que d’une part les données soient transmises à un organe récepteur prêt à les recevoir, et que d’autre part l’organe émetteur soit informé que les données sont bien parvenues à destination. Par exemple STROBE et ACKNOLEDGE pour une imprimante ou DTR et DSR pour un Modem.

Signaux circulant entre le circuit d’interface et le processeur

* des données par le bus de données qui transporte les données proprement dites et les mots d’état.

* des adresses par le bus d’adresse : deux ou trois fils pour la sélection des différents registres interne du circuit, registre de données, de commande, d’état, etc.

* un ou plusieurs fils pour la sélection de l’interface qui dispose à cet effet d’une ou plusieurs broches de « sélection de boîtier » (chip select). Ces broches ne sont pas directement reliées au processeur mais au circuits de décodage d’adresses

* des demandes d’interruption.

* des commandes particulières :

par exemple: remise à zéro des registres de l’interface (RESET).

Les principaux registres internes.

Trois types de registres sont présents dans la plupart des interfaces.

* Registre de données :

Le micro écrit ou lit la donnée à transmettre ou reçue dans ce registre.

* Registre de commande :

Ce registre permet de configurer, de programmer l’interface afin de l’adapter au périphérique.

* Registre de statut ou d’état :

Ce registre informe le microprocesseur de « l’état » du périphérique via les lignes de dialogue et de contrôle. Par exemple données disponibles, pas prêt à émettre, etc…

Exemple d’interface le PIO (la gestion du clavier n ‘est pas réalisé de cette façon là dans le PC)

8.4.2 Gestion d’une interface d’E/ S.

Chaque registre interne d’un circuit d’E/S possède une adresse dans la memory map du processeur, ainsi la sélection d’une entrée/sortie se fait comme pour la mémoire :

1. Le micro-processeur génère l’adresse du Port d’E/S ainsi que l’ordre d’écrire ou de lire.

2. La logique de décodage génère un chip select vers le circuit d’E/S désigné.

3. La donnée est lue ou écrite dans un registre du port, via le bus de données.

C’est le circuit d’interface qui se charge de transmettre la donnée au périphérique.

Note : Le timing est du même type que pour l’accès à une casse mémoire.

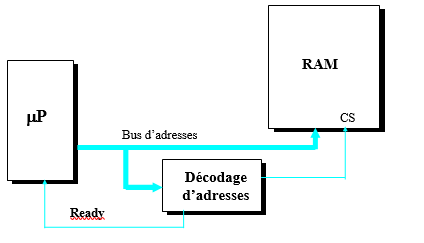

8.5 Les circuits de décodage d’adresses.

Le concepteur d’un système à base de microprocesseur doit « positionner » chacun des différents boîtiers constituant la RAM, la ROM et les E/S dans la memory map (ensemble des adresses gérées par le processeur) de sorte qu’ils ne se « chevauchent » pas (voir schéma); c’est le rôle d’un ensemble de circuits que l’on regroupe sous le nom de Décodage d’Adresses.

Ce sous-ensemble est connecté d’un coté au bus d’adresses du µP et de l’autre aux broches CS, pour Chip Select (sélection du boîtier), de chaque circuit mémoire ou d’interface.

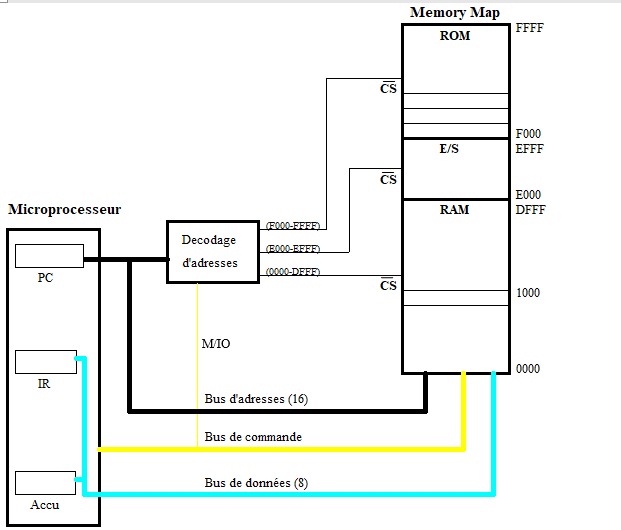

Système qui utilise un processeur de type 6809

(la mémoire et les E/S sont gérés dans un espace mémoire unique)

Dans l’exemple précédent, lorsque le µP émet une adresse correspondant à la RAM, soit une adresses comprises entre 0000 et DFFF, le décodage d’adresses positionne le CS de celle-ci à 0 (actif) et tous les autres à 1 (inactif). De ce fait, tous les boîtiers autres que la RAM sont mis en haute impédance et ainsi déconnectés du bus de données.

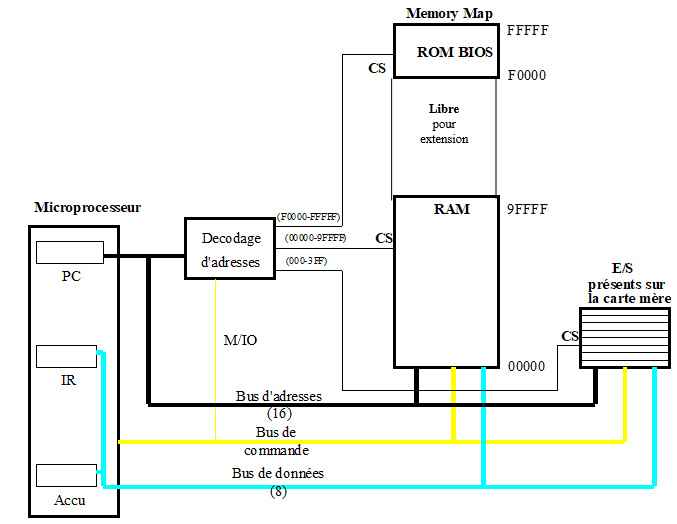

Principe de l’adressage d’un PC (micro de la famille 8086)

Les processeurs Intel du 8086 au Pentium gèrent deux espaces mémoires distincts : un pour les différentes mémoires (1 Mo pour le 8086 et les autres processeurs lorsqu’ils travaillent en mode réel) et un pour les circuits d’E/S de 64 Ko La sélection de l’un ou de l’autre espace se fait en fonction de l’instruction exécutée par le processeur, les instructions travaillant sur les E/S positionnent la broche M/IO à 0 alors que les autres instructions positionnent cette même broche à 1.

8.6 Circuits d’horloge.

Le microprocesseur travaille au rythme d’une horloge qui peut être interne au processeur ou réalisée par un circuit externe. Tous les échanges entre le µP et les différents boîtiers externes se font au rythme de cette horloge.

9 – TECHNIQUES D’INTERFACAGE.

9.1 Généralités

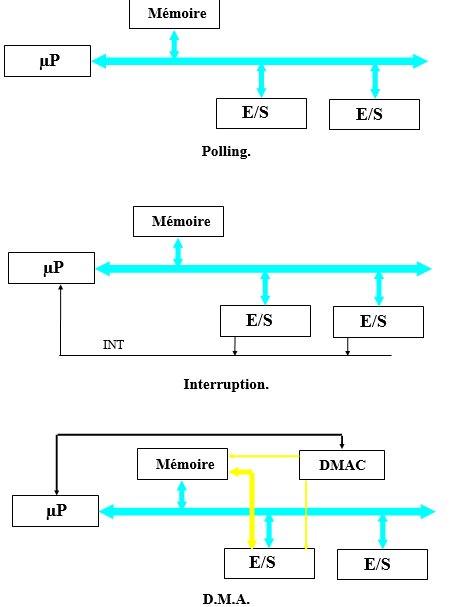

Les trois techniques de base de gestion des circuits d’entrée/sortie sont :

1. La gestion des entrées/sorties par programme (Polling).

2. La gestion des entrées/sorties par interruptions.

3. L’accès direct à la mémoire (DMA).

9.2 Le « Polling » ou mode programmé

Le mode programmé se caractérise par un transfert de données à l’initiative du programme exécuté par le processeur.

Des signaux de commande et d’état entre l’interface et le périphérique permettent de gérer le dialogue.

Prenons, par exemple, le cas d’une imprimante connectée à un port de type PIO, ce sont les lignes « strobe » et « acknoledge » qui gèrent le dialogue.

Le principe de fonctionnement est le suivant, le µP via le PIO émet un code ASCII vers l’imprimante et positionne la ligne strobe; l’imprimante, qui teste en permanence l’état cette ligne, « sait » qu’une donnée est disponible et donc la récupère, puis après un temps qui dépend de sa vitesse de traitement elle émet un acknoledge qui signale qu’elle est prête à nouveau à recevoir une donnée.

Le processus de transfert est le suivant :

* Lecture du mot d’état du port du PIO affecté à l’imprimante;

* Test du signal d’état « prêt », le bit correspondant à acknoledge.

* Si « prêt », écriture du code ASCII dans le registre de données du port qui le transmet à l’imprimante.

* Positionnement à l’état vrai du bit correspondant à la ligne strobe dans le registre de commande du port.

9.3 Les interruptions

Les interruptions permettent une meilleure utilisation du micro-processeur. Ce mécanisme permet à n’importe quelle interface d’envoyer un signal (une impulsion) sur une broche du micro-processeur appelée INT ou IRQ (demande d’interruption). Le micro-processeur interprète cette impulsion comme une requête de service par un périphérique.

Lorsque plusieurs interfaces ou circuits externes sont susceptibles de demander une interruption, il faut pouvoir reconnaître le circuit qui a demandé l’interruption. Cette reconnaissance est rendue encore plus difficile par le fait que deux ou plusieurs interruptions peuvent se produire au même moment. Une solution très simple est possible lorsque le microprocesseur possède deux, trois ou plusieurs entrées d’interruption avec un ordre de priorité entre elles (en cas d’interruptions simultanées) et à condition que le nombre de périphériques ou de circuits externes susceptibles de demander une interruption ne dépasse pas le nombre d’entrées INT. A titre d’information, signalons que le micro-processeur Z80 possède trois niveaux d’interruption hiérarchisés. Le câblage est alors très simple.

Le passage au niveau 1 de l’une des entrées INTREQ branchera le micro-processeur sur un sous-programme spécifique du périphérique ayant fait la demande d’interruption.

Pour ce faire, des adresses sont réservées pour traiter les interruptions (voir figure ci-dessous). Ces adresses contiennent, pour chaque entrée d’interruption, l’adresse du programme de traitement correspondant, elles se nomment vecteurs d’interruption.

Exemple : 6809.

Lorsque le 6809 reçoit une NMI, il va chercher aux adresses FFFC et FFFD l’adresse du programme correspondant au traitement de la NMI.

|

FFFF-FFFE |

RESET |

|

|

FFFD-FFFC |

NMI |

|

|

FFFB-FFFA |

SWI |

|

|

FFF9-FFF8 |

IRQ |

|

|

FFF7-FFF6 |

FIRQ |

|

|

FFF5-FFF4 |

SWI2 |

|

|

FFF3-FFF2 |

SWI3 |

Vecteurs d’interruption 6809.

Lorsqu’il y a plus d’interfaces autorisées à demander une interruption que le microprocesseur ne possède de broches d’interruption, il faut :

* Soit réunir les demandes d’interruption en ou câblé et rechercher le périphérique qui a fait la demande par une scrutation identique à celle que nous avons vue pour le mode programmé : c’est le mode interruptible avec test d’état.

* Soit utiliser un circuit spécial de traitement des interruptions (PIC) : c’est le mode « interruptible » vectorisé (cas du PC).

Dans le mode « interruptible » avec test d’état toutes les demandes d’interruption sont réunies en ou câblé à l’entrée INT du micro-processeur. Dès que cette entrée passe au niveau logique vrai « 1 » ou « 0 » par suite d’une demande d’interruption, le micro-processeur termine l’instruction en cours puis se branche à un sous-programme de recherche du périphérique qui a demandé l’interruption ou du périphérique prioritaire en cas de plusieurs demandes simultanées.

Pour cela le micro-processeur devra lire successivement les registres d’état des interfaces susceptibles d’interrompre.

Un bit dans le registre d’état des interfaces est mis à 1 lorsqu’il y a demande d’interruption. La recherche terminée, le micro-processeur exécute le sous-programme d’E/S spécifique du périphérique.

Remarque :

L’ordre de lecture des mots d’état des interfaces détermine la hiérarchisation des priorités, celle-ci est donc définie dans le sous-programme de recherche « Polling ».

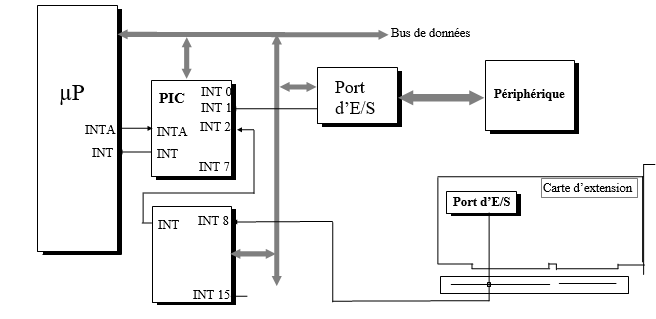

Utilisation d’un circuit spécialisé PIC (cas du PC XT).

Utilisation de deux PIC montés en cascade (cas d’un PC actuel).

Les demandes d’interruption arrivent sur un circuit spécialisé, un contrôleur d’interruption programmable, qui assure la hiérarchisation des priorités. Pour chaque demande qui lui parvient, il effectue à son tour une demande d’interruption au microprocesseur. Celui-ci, lorsqu’il à terminé l’instruction en cours, envoie un signal INTA (Interrupt acknowledge) qui est une reconnaissance de la demande d’interruption. Le contrôleur d’interruption envoie, alors, via le bus de données le numéro de l’interruption. Le microprocesseur utilise ce numéro pour rechercher l’adresse du vecteur d’interruption, puis lit ce vecteur et exécute le programme correspondant.

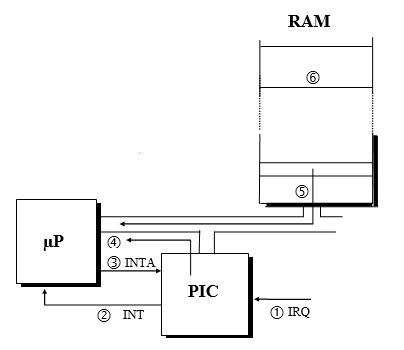

Résumé du traitement d’une interruption (cas du PC) :

Un circuit d’E/S fait une demande d’interruption.

Le PIC positionne sa ligne INT pour le signaller au µP.

Après avoir terminé l’exécution de l’instruction en cours et avoir sauvegardé ses # registres internes, le µP positionne sa ligne INTA.

Le PIC dépose sur le bus de données le N° d’INT associé à l’interruption. (ex : 9H).

Le µP calcul (N° x 4) l’adresse mémoire correspondant au N° d’INT (dans l’exemple 24H). Puis lit le contenu de ces cases (4) afin de récupérer l’adresse logique du programme d’interruption.

Le µP exécute le programme d’interruption dont le rôle est de gérer le périphérique relié à l’interface.

A la fin du programme d’INT une instruction (IRET) oblige le µP à récupérer ses # registres et ainsi reprendre le déroulement de son programme.

Il reste un seul problème: c’est celui de l’arrivée d’une interruption de forte priorité en cours d’exécution d’une interruption de plus faible priorité. Un comparateur digital intégré dans le PIC compare le niveau de priorité de toute interruption se signalant avec celui de l’interruption en cours d’exécution s’il y en a une. Les niveaux de priorités sont contenus dans un registre spécialisé du contrôleur d’interruption programmé par le microprocesseur.

Dans le cas de l’arrivée d’une interruption plus prioritaire que celle qui est en cours d’exécution, le PIC fait une demande d’interruption au microprocesseur et par suite le sous-programme de l’instruction prioritaire est exécuté.

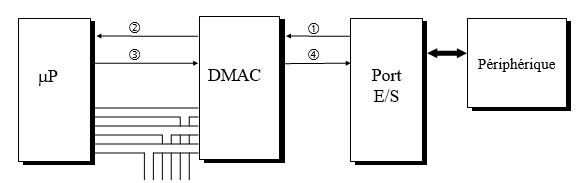

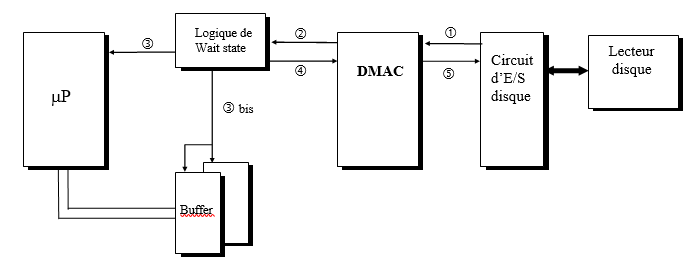

9.4 Accès direct à la mémoire (D.M.A)

Certains périphériques échangent un grand nombre d’informations avec la mémoire (exemple disque dur). L’utilisation d’une méthode traditionnelle d’échange entre le périphérique et la mémoire aurait pour conséquence un temps de transfert trop important. Dans ce cas on utilise le mode d’accès direct à la mémoire.

Le micro-processeur est mis temporairement en « sommeil » (3ème état) par un circuit spécifique, le contrôleur de D.M.A, qui réalise le transfert des données en prenant le contrôle des différents bus.

Il existe plusieurs façons de réaliser un accès direct mémoire :

9.4.1 Arrêt du processeur (3ème état)

- Une interface demande un transfert au contrôleur de D.M.A. Ceci suite à un ordre du microprocesseur.

- Le contrôleur de D.M.A prévient le micro-processeur par une ligne du bus de commande.

- Le micro-processeur se « déconnecte » des bus et prévient le D.M.A.C qu’il peut effectuer le transfert.

- Le D.M.A.C prévient le périphérique que le transfert va s’effectuer.

- Le D.M.A.C réalise le transfert en prenant le contrôle des 3 bus.

- A la fin du transfert le contrôleur de DMA « réactive » le microprocesseur.

Accès direct mémoire par arrêt du processeur

9.4.2 Vol de cycle.

Une ligne de contrôle stoppe le micro-processeur (plus précisément le met en attente) en suspendant l’exécution de l’instruction en cours à l’intérieur de son cycle. L’horloge interne du processeur est arrêtée; les lignes des différents bus sont mises en 3ème état. Le contrôleur DMA prend la relève et « vole » plusieurs cycles machines pour que s’effectue le transfert de données. A la fin du transfert, les lignes de contrôle sont rétablies, l’horloge redémarre ce qui permet au processeur de terminer son cycle.

La seule conséquence de cette « interruption » de l’exécution de l’instruction est un allongement du temps apparent de son exécution.

Cette technique est encore utilisée dans les PC actuels pour les opérations de transfert disquette.

Accès direct mémoire par vol de cycle

Accès direct mémoire par vol de cycle

LE MICROPROCESSEUR ET SON ENVIRONNEMENT (SOFTWARE)

===============================

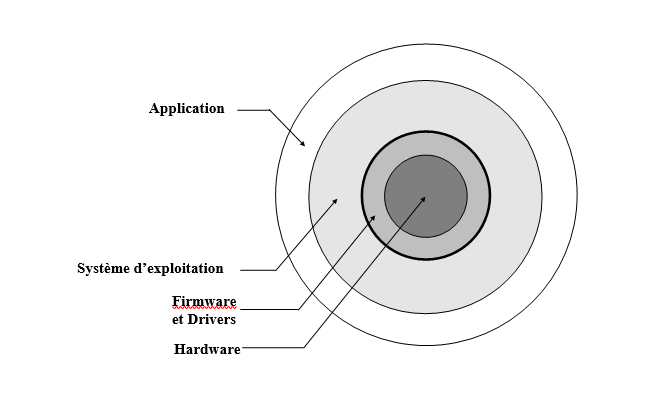

1 – LES DIFFERENTES COUCHES DU LOGICIEL D’UN MICRO-ORDINATEUR.

1.1 Le Hardware (couche 1) :

Regroupe l’ensemble de l’équipement que constituent un micro-ordinateur (circuits intégrés, composants divers, micro-processeurs, périphériques…).

1.2 Le Firmware (couche 2) :

Désigne l’ensemble des routines, programmes implantés d’origine sur la carte mère en ROM. Le Firmware sert d’interface logicielle entre le matériel et le système d’exploitation. Son rôle consiste à contrôler, gérer les différents circuits d’interface de l’ordinateur.

Note:

Dans le cas de périphériques qui ne sont pas « prévus » dans la configuration de base (scanner, carte son, carte réseau, …) on charge en RAM un petit programme que l’on appelle Driver qui réalise l’interface entre le matériel lié a ce périphérique et le logiciel des couches supérieurs.

1.3 Le Software (couche 3 – 4) :

Regroupe tous les produits de type logiciels, la plupart sont stockés sur une unité de sauvegarde externe dans des fichiers.

* Le système d’exploitation (couche 3) :

Regroupe un ensemble de fonctions, toutes destinés à coordonner les opérations nécessaires à la mise en oeuvre des programmes. Il gère aussi les unités de sauvegarde (disquette, disque dur).

* Les utilitaires et les langages de programmation (couche 4) :

Un micro-ordinateur est livré avec des programmes utilitaires par exemple un éditeur de texte, un debogueur, etc… et la plupart du temps avec un ou plusieurs langages de programmation par exemple: assembleur, basic…

* Les programmes d’applications (couche 4):

Ces programmes, écrits grâce à un langage de programmation, sont spécifiques par exemple : traitement de texte, comptabilité, tableur, gestionnaire de base de données…

2 – LE SYSTEME D’EXPLOITATION.

Le système d’exploitation « offre » à l’utilisateur un certain nombre de commandes qui lui permette d’utiliser son micro-ordinateur par exemple :

– Le formatage du support de sauvegarde.

– La gestion des données et des fichiers.

– Le « lancement » de programme.

– La gestion des interruptions.

– La gestion des périphériques d’entrées/sorties (paramètrage).

– La gestion des erreurs.

– La protection de la mémoire.

Il existe plusieurs grandes familles de système d’exploitation :

2.1 Les systèmes mono-tâches :

Ce type de système d’exploitation ne peut exécuter qu’un seul programme (tâche) à la fois. Exemple : MSDOS, CPM…

Le programme une fois chargé en mémoire est exécuté séquentiellement puis le Système d’exploitation reprend le contrôle du système.

2.2 Les systèmes multi-tâches :

La notion de multi-tâche permet d’exploiter au maximum les capacités du micro-processeur, il est possible de traiter plusieurs programmes simultanément. En réalité, le micro-processeur ne peut réaliser qu’une seule chose à la fois. L’astuce dans les systèmes multi-tâches consiste à lui faire exécuter pendant un temps très court un petit fragment du programme 1, puis à le faire passer au programme 2, et ainsi de suite. L’utilisateur à l’impression que toutes les tâches sont exécutées simultanément. Exemple : OS 2, Windows 95, Windows NT et d’une certaine manière Windows 3.x qui est un sur-ensemble de MSDOS.

2.3 Les systèmes multi-utilisateurs :

Plusieurs utilisateurs à travers des terminaux peuvent accéder aux ressources de l’ordinateur. Ceci rejoint un peu le multi-tâche, dans le sens ou le micro-processeur partage son « temps » entre plusieurs utilisateurs donc plusieurs programmes. Exemple UNIX, XENIX, PROLOG.

3 – LES LANGAGES DE PROGRAMMATION.

3.1 Qu’est qu’un programme ?

Un programme est une suite d’instructions écrites dans un certain langage.

L’exécution du programme par le système se fera de façon séquentielle (une instruction après l’autre).

Le rôle du programmeur est de décomposer la tâche à effectuer en une suite d’opérations élémentaires, sous la forme d’un organigramme ou en pseudo-langage, voir exemple de l’horloge numérique, puis de le traduire en une suite d’instructions propres au langage utilisé (exemples le Basic, l’Assembleur, Pascal).

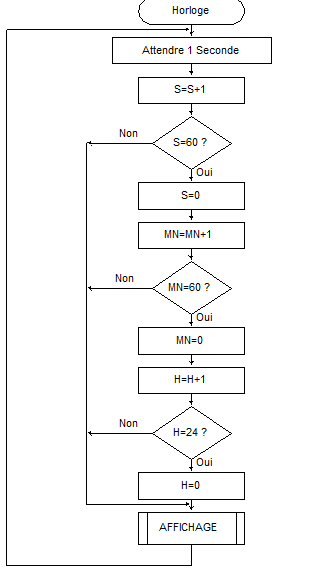

Exemple de Programme écrit en pseudo langage – HORLOGE NUMERIQUE

1 – Temporiser 1 seconde.

2 – Ajouter 1 aux secondes.

3 – Est-on arrivé à 60 s ?

4 – Si non, aller à 14.

5 – Si oui, mettre les secondes à zéro.

6 – Ajouter 1 aux minutes.

7 – Est-on arrivé à 60 mm ?

8 – Si non, aller à 14.

9 – Si oui, mettre les minutes à zéro.

10 – Ajouter 1 aux heures.

11 – Est-on arrivé à 24 h ?

12 – Si non, aller à 14.

13 – Si oui, mettre les heures à zéro.

14 – Afficher.

15 – Recommencer en 1.

Organnigramme du même programme

3.2 Qu’est-ce qu’un langage de programmation ?

C’est un « outil » qui permet au programmeur d’écrire un programme afin de faire exécuter à un ordinateur des tâches très diverses, depuis un programme de comptabilité jusqu’à la gestion d’un processus industriel.

Il existe de nombreux langages de programmation, chacun ayant ses caractéristiques. Ils sont classés généralement en deux groupes :

– les langages dits de « bas niveaux », qui sont proches de la machine et lié à ses structures interne (en particulier chaque micro-processeur possède son propre langage machine). On trouve à ce niveau le langage machine et l’assembleur.

– Les langages de « haut niveau » dits évolués qui « s’écartent » de la machine et de ses structures internes et qui se rapproche de l’expression orale. On y trouve, entre autres, le Fortran, le Pascal, le Basic, le Cobol, le C, l’ADA, etc…

3.3 Interpréteurs et compilateurs

Les différents langages dit de haut niveau nécessitent tous une traduction du texte du programme en instructions du micro-processeur. Il y a deux façons différentes de réaliser cette opération :

– L’interpréteur traduit et exécute ligne après ligne le programme. Toutes les instructions sont testées et exécutées une à une. L’exécution du programme nécessite alors l’implantation simultanée de l’interpréteur et du programme.

– Le compilateur traduit au préalable le programme source en un programme objet qui sera directement exécutable par le micro-processeur.

3.4 Les langages existants.

3.4.1 Langage machine et assembleur.

Un peu d’histoire. Dans les années 46-48, la mise en oeuvre du logiciel consistait à basculer une longue suite d’interrupteurs sur un panneau de commande. On « entrait » ainsi, les unes après les autres, des instructions codées en binaires (0 ou 1). Ceci était fastidieux et source d’erreurs. On eut l’idée de regrouper les bits par 3 ce qui permit d’entrer le programme en OCTAL, puis on regroupa les bits par 4 (c’est toujours le cas aujourd’hui) ce qui donna l’HEXADECIMAL, ainsi un OCTET s’écrit avec 2 chiffres: 255 s’écrit FF. Dans les années 60, on entrait un programme en hexadécimal (langage machine), cette méthode est encore utilisée sur les petits kits.

L’introduction de l’assembleur à amélioré considérablement la programmation en associant un MNEMONIQUE au code machine.

Exemple :

MOV AX,B000 signifie: mettre la valeur B000 dans AX

s’écrit en langage machine B8 00 B0.

IN AL,61 signifie: mettre dans AL le contenu du port D’E/S

61H s’écrit EA 61.

Le programmeur, en assembleur, écrit son programme en utilisant les mnémoniques puis « lance » un programme que l’on nomme Assembleur, dont le rôle est de traduire la totalité des instructions en langage machine, seul langage que « comprend » le microprocesseur.

Chaque microprocesseur possède son propre langage machine, il existe donc un langage assembleur par microprocesseur. Les programmes ainsi écrits ne pourront être exécutés que sur un seul type de machine (par exemple les compatibles IBM – PC).

Un programme écrit grâce à un assembleur, s’il est plus difficile à mettre au point, est plus rapide et plus compact qu’un programme écrit avec un langage évolué, par contre un programme écrit en langage évolué est « PORTABLE », cela veut dire qu’il peut être exécuté sur des machines différentes.

3.4.2 Langages évolués.

* Le Pascal

Ce langage est un dérivé de l’ALGOL 60. Ce langage est structuré et très stricte dans sa syntaxe. La version Turbo Pascal est la plus répandue sur les PC.

* Le langage C

Le langage C a été développé chez BEL Laboratories pour écrire le système d’exploitation UNIX. Sa syntaxe se rapproche du Pascal. Le C a été conçu pour remplacer l’assembleur pour des développements au niveau système. Certains opérateurs et instructions sont très proches des instructions du langage machine, mais ses structures de données et l’architecture de ses programmes en fait un langage de haut niveau.

* Le Basic

Le Basic est un langage universel qui existe en version interpretée et compilée. Il est relativement lent et n’est pas un langage structuré.

* Le Cobol

Ce langage relativement ancien, 1955 environ, est très utilisé dans les programmes de gestion sur les gros ordinateurs ainsi que sur les mini-ordinateurs.

* Le Fortran

Ce langage est lui aussi relativement ancien, 1956 environ, il est très utilisé pour les applications scientifiques.

Voici 2 exemples de langage, dans l’ordre Assembleur, Pascal.

|

; définition des constantes cr equ 13 ;retour chariot lf equ 10 ;line feed ;_____________________________________________________ prog segment assume cs:prog org 100h debut: jmp begin ;_____________________________________________________ ;définition des données mes1 db « Appuyer sur la touche ( 0 ou 1 ) ou 9 pour arrêter »,cr,lf, »$ » mes2 db « Vous avez appuyé sur 0″,cr,lf, »$ » mes3 db « Vous avez appuyé sur 1″,cr,lf, »$ » ;_______________________________________________________ begin: mov ax,cs mov ds,ax ;initialisation de DS boucle: lea dx,mes1 ;mov dx,offset mes1 mov ah,09 int 21h ;appel INT DOS affichage message att: mov ah,00 int 16h ;appel INT BIOS attente d’une touche sans echo cmp al, »9″ je retdos cmp al, »0″ je touch0 cmp al, »1″ jne att ;—— touche 1 ——– mov dx,offset mes3 mov ah,09 int 21h ;affichage message mes3 jmp boucle ;______ touche 0 ——– touch0: mov dx,offset mes2 mov ah,09 int 21h ;affichage message mes2 jmp boucle ;—— retour au MSDOS —— retdos: mov ah,4Ch ;appel INT DOS retour au MSDOS int 21h prog ends end debut |

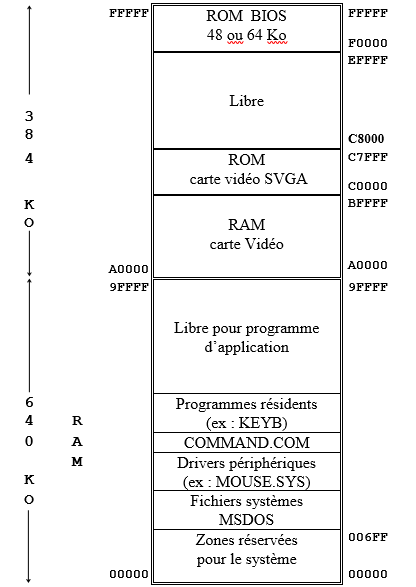

4 – Organisation mémoire d’un PC.

Les compatibles PC XT sont équipés de processeurs 8088/86 qui permet d’adresser 1 Mo de mémoire (1048576 octets) grâce à ses 20 fils d’adresses. Ces emplacements sont numérotés en hexadécimal de 00000H à FFFFFH. Les PC AT sont équipés du 80286, 80386, 80486 ou du Pentium, ce qui dans une première approche ne change rien car le MSDOS les fait fonctionner en mode réel. Dans ce mode ces microprocesseurs se comportent comme des 8086, bien sûr plus rapide.

Cette mémoire est subdivisée en bloc, chaque bloc ayant une fonction précise.

4.1 Organisation des 384 Ko supérieurs de la memory map.

* De 64 Ko à 128 Ko selon le modèle et le type de BIOS sont réservés à la ROM BIOS (Basic Input Output System) dans le dernier segment[10]1 compris entre F0000 et FFFFF.

Remarque :

Sur un AT cette mémoire est aussi accessible dans le segment compris entre FF0000 et FFFFFF afin de garder une compatibilité entre le mode protégé et le mode réel.

Le BIOS pour Basic Input Output System englobe un ensemble de programmes qui entre autre « gèrent » les organes d’entrée/sorties.

Une des tâches du BIOS est, donc, de fournir les routines d’entrée/sortie (programmes initialisant et gérant les divers circuits d’interface). Ces routines sont accessibles par le programmeur par l’appel d’interruptions logiciels, de 10H à 1FH.

Tout concepteur de système d’exploitation doit impérativement utiliser ces routines.

Ces différentes fonctions assurent, de ce fait, une interface standard entre le système d’exploitation et le matériel (hardware) qui n’est pas à 100 % identique d’un compatible à l’autre.

Les variables utilisées par le BIOS sont situées en RAM aux adresses comprises entre 400H et 4FFH.

La deuxième tâche du BIOS consiste à lancer le système lors de la mise sous tension.

Le microprocesseur, lors de la mise sous tension ou lors d’un Reset, exécute le programme qui commence à l’adresse FFFF0 (F000:FFF0). A cette adresse une instruction exécute un saut à une routine dont l’adresse peut varier d’un PC à l’autre, elle réalise par contre sensiblement les mêmes tâches:

– Tester les différentes fonctions du microprocesseur; ses registres et quelques instructions sont testées.

– Tester la ROM BIOS.

– Tester les différents circuits de la carte mère, tels le contrôleur de DMA, le contrôleur d’interruption, les RAM, etc.

– Initialiser la table des vecteurs d’interruption ainsi que les variables du BIOS.

– Tester les périphériques, clavier, lecteur de disquette, carte vidéo, etc.

– Rechercher des éventuelles extensions ROM, qui contiennent les programmes de gestion de périphériques tels le contrôleur de disque SCSI, la carte vidéo (EGA-VGA), etc.

Une ROM d’extension doit toujours commencer par les codes 55H et AAH. Le BIOS « appelle » ces routines par un CALL FAR, ce qui permet, entre autre, au programme contenu dans cette ROM de rediriger des vecteurs d’interruptions vers ses propres routines.

– Charger le système d’exploitation. C’est le rôle de l’interruption 19H , appelée lorsque l’on actionne simultanément les touches Alt, Ctrl, Suppr.

Cette routine charge un secteur en RAM qui doit être situé à un emplacement bien précis de la disquette ou du disque dur. Ce secteur contient une routine qui à son tour chargera le reste du système d’exploitation.

* Les adresses comprises entre C0000 et EFFFF ne sont pas utilisées en standard, les constructeurs de cartes d’extension peuvent les utiliser. Par exemple la ROM de la carte VGA est située entre C0000 et C7FFF. Ces ROM qui sont des extensions du BIOS sont reconnues automatiquement par le programme d’initialisation de la ROM BIOS.

* Les adresses comprises entre A0000 et BFFFF sont réservées pour la mémoire vidéo. Les adresses comprises entre A0000 à AFFFF sont réservées à la RAM vidéo des cartes VGA et SVGA en mode graphique, de même que les adresses comprises entre B8000 et BFFFF sont utilisées par les cartes VGA et SVGA en mode texte.

4.2 Organisation des 640 Koctets de la RAM.

* Les 640 K octets de mémoire restante sont occupés par la RAM de travail. Certaines adresses de la RAM sont réservées par le système.

* Les adresses basses de la RAM de 00000 à 006FF sont réservées par le système. Il y stocke des informations nécessaires à son bon fonctionnement :

– Les vecteurs d’interruptions généraux (Hardware).

– Les vecteurs d’interruptions du BIOS.

– Les vecteurs d’interruptions du DOS.

– Enfin des tables de données nécessaires aux différents programmes du BIOS du DOS.

* Une zone mémoire de taille variable, selon la configuration, est réservée par le MSDOS pour y stocher des programmes, en particulier :

– Les fichiers MSDOS (IBMBIO.COM, IBMDOS.COM, COMMAND.COM).

– Les pilotes (drivers) de périphériques et les gestionnaire de mémoire (Mouse.sys, Himem.sys, EMM386.exe, etc).

– Les programmes résidents (TSR), Keyb, Doskey, etc).

-

Nous verrons que la nouvelle génération de processeur est capable de traiter plus d’une instruction dans un même cycle (architecture superscalaire) ↑

-

aussi appelé Opcode. ↑

-

Plusieurs milliers de fois par seconde ↑

-

Fast Page Mode ↑

-

Extended Data Out ↑

-

Synchronous DRAM ↑

-

Direct Rambus DRAM ↑

-

Tous ces circuits sont intégrés dans un ou deux circuits que l’on appelle le chip set sur les cartes mères actuelles. ↑

-

Le coprocesseur arithmétique est intégré dans le processeur depuis le 486 DX. ↑

-

1 Un segment est une zone mémoire de 64 Ko. ↑