- PROCESSEUR

- ARCHITECTURE INTERNE DU PROCESSEUR

- ARCHITECTURE DES PROCESSEURS POUR MICRO-ORDINATEURS

- JEU D’INSTRUCTION DU PROCESSEUR

- ARCHITECTURES EVOLUEES

- TECHNOLOGIE DES MICROPROCESSEURS

- ANNEXES

-

- Modes de fonctionnement des processeurs Intel

- Exemple de jeu d’instructions

- EXERCICES

PROCESSEUR

C’est quoi le processeur de l’ordinateur ?

Un processeur est un ensemble matériel destiné, dans un ordinateur ou une autre machine, à interpréter et exécuter des traitements. Cet organe peut être généraliste et constituer le processeur central d’un ordinateur (par exemple, le Pentium) ou spécialisé dans des tâches particulières ; par exemple, un processeur DSP (Digital Signal Processor) est spécialisé dans le traitement des signaux numériques.

Le processeur central peut être vu comme le cerveau (c’est la partie la plus « intelligente ») ou comme le coeur (qui pompe des instructions et expulse des données, et non du sang) de l’ordinateur ; il est aussi appelé :

UCT (Unité Centrale de Traitement) ou CPU (Central Processing Unit) dans un gros système,

microprocesseur dans un micro-ordinateur (processeur tenant tout entier sur une seule puce de silicium et contenant plusieurs millions de composants électroniques).

Le processeur central remplit les fonctions suivantes :

Décodage et exécution des instructions contenues dans les programmes, en passant par un stockage intermédiaire dans des registres.

Lecture/écriture des données en mémoire.

Commande des autres éléments de l’ordinateur, contrôle des opérations d’entrée/sortie (clavier, souris,…), et gestion des unités de stockage et des périphériques.

HORLOGE

Les ordinateurs sont des machines synchrones, ils sont cadencés par une horloge (c’est-à-dire qu’une instruction élémentaire du processeur nécessite un nombre entier de cycles d’horloge).

L’horloge (ou générateur de signal d’horloge) est une puce de la carte mère basée sur un oscillateur qui utilise un cristal de quartz. Le rythme du quartz est divisé pour obtenir le rythme de l’ordinateur. Tel les battements d’un coeur, l’horloge rythme donc la vie de l’ordinateur en génèrant la cadence qui sert de cycle de base pour le fonctionnement de l’ordinateur (processeur et autres circuits tels que le Timer).

La fréquence d’horloge est mesurée en Méga-Hertz (MHz), le Hertz étant l’unité qui correspond à la fréquence d’un phénomène dont la période est une seconde.

La vitesse d’horloge (en MHz) donne la durée de chaque cycle machine, c’est-à-dire l’intervalle de temps au cours duquel le processeur transfère l’adresse d’un mot sur le bus adresses et recherche en mémoire la donnée demandée qu’il charge sur le bus données. La vitesse d’horloge a tendance à augmenter avec les générations de processeurs. Par exemples, pour les microprocesseurs Intel, …

|

processeurs |

fréquences |

||

|

anciens |

8088 |

4.77, 8, 10 |

|

|

8086 |

8, 10 |

||

|

80286 |

6, 8, 10, 12, 16, 20 |

||

|

386SX |

16, 20, 25 |

||

|

386DX |

16, 20, 25, 33 |

||

|

486SX |

25, |

33 |

|

|

486DX |

25, 33, 50, 66, 75, 100 |

||

|

actuels |

Pentium |

(60, 66, 75, 90, 100, 120), 133, 150, 166, 200 |

|

|

Pentium Pro |

150, 180, 200 |

||

|

MMX (Pentium) |

166, |

200 |

|

|

Klamath (Pentium Pro) |

233, |

266 |

|

Le Timer (ou horloge programmable) est un circuit de la carte mère utilisant l’horloge afin de générer des signaux tous les x cycles d’horloge (il est dit « programmable » car cette fréquence peut être modifiée). Ce circuit permet au processeur de maintenir l’heure et la date système lorsque le système est sous tension (une batterie permet la maintenance hors tension). Le timer est exploité pour produire des signaux horaires réguliers à de nombreuses fins, y compris pour générer des sons sur le haut parleur.

STRUCTURE EXTERNE D’UN MICROPROCESSEUR

Vu de l’extérieur, un microprocesseur se présente sous la forme d’un boîtier comprenant un certains nombre de broches.

Les broches permettent au processeur de communiquer avec les composants de la carte mère. Chaque broche est généralement dédiée à une tâche unique, par exemple …

-

- alimentation,

- bus de données et d’adresses,

- gestion du bus (demande/autorisation d’accès au bus par un circuit extérieur, signal de lecture/écriture d’une donnée mémoire ou d’entrée/sortie,…),

- contrôle du processeur (horloge, initialisation, interruption,…).

Le nombre de broches (et donc les possibilités de communications) ont tendance à augmenter avec les générations de processeurs. Par exemples, pour les microprocesseurs Intel, …

|

processeurs |

nombre de broches |

|

|

anciens |

8088/8086 |

40 |

|

80286 |

68 |

|

|

386SX |

100 |

|

|

386DX |

132 |

|

|

actuels |

486 |

168 |

|

Pentium |

273 |

|

|

Pentium Pro |

390 |

Les boîtiers processeurs peuvent être soudés sur la carte mère, ou inséré sur un support. Pour un processeur inséré sur un support, il peut être extractible à l’aide d’un outil spécial évitant de tordre ou de casser les pattes (par exemple, PGA), ou doté d’un levier permettant une extraction aisée sans outils spéciaux (support ZIF : Zero Insertion Force).

ARCHITECTURE INTERNE DU PROCESSEUR

Quels sont les composants d’un processeur ?

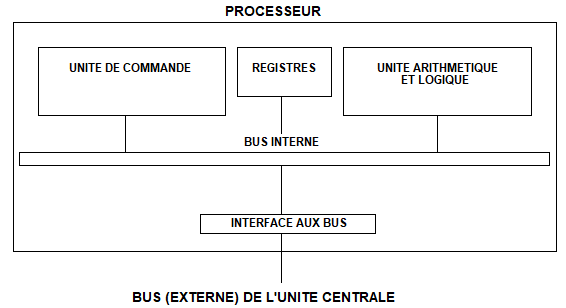

Un processeur est constitué au minimum :

d’une unité de commande qui coordonne le fonctionnement,

d’une unité arithmétique et logique qui effectue les traitements, des registres qui permettent un stockage local.

REGISTRES

Un registre est une petite mémoire spécialisée (interne au processeur) offrant la possibilité de garder en mémoire dans le processeur lui-même un certain nombre d’informations, afin d’effectuer des traitements complexes sans avoir à attendre un transfert d’octets depuis la mémoire centrale. Les transferts de données entre les registres passent par le bus de données interne au processeur, ce qui les rend très rapides par rapport aux accès à la mémoire centrale qui transitent par le bus externe.

Le nombre (quelques dizaines) et la taille des registres est une des caractéristiques du processeur.

Lorsqu’on dit qu’un microprocesseur a une architecture 8, 16, 32 bits ou 64 bits, on fait généralement référence à la taille de ses registres et de son bus interne de données . La taille des registres détermine la complexité, la quantité et le débit des informations que le processeur est capable de prendre en compte en une seule opération.

|

processeur |

taille des registres (en bits) |

|

|

8088 |

16 |

|

|

8086 |

16 |

|

|

80286 |

16 |

|

|

80386 |

32 |

|

|

486 |

32 |

|

|

Pentium |

32 et 64 |

|

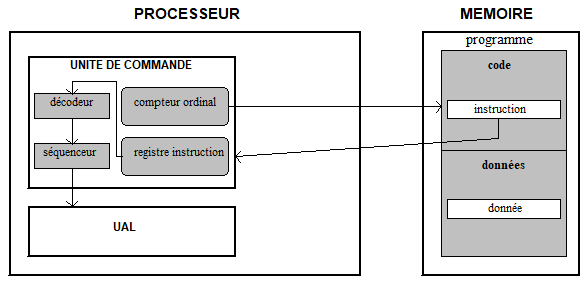

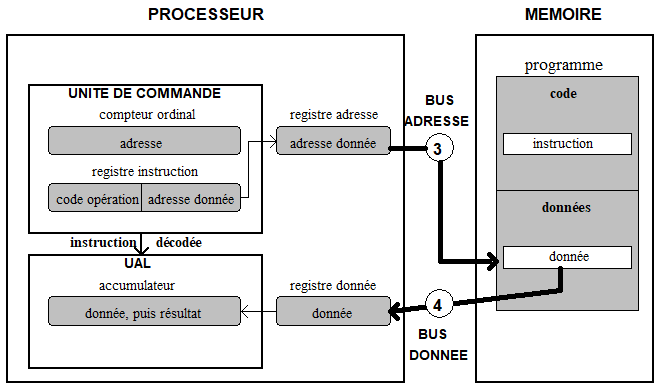

UNITE DE COMMANDE (UC) ET UNITE ARITHMETIQUE ET LOGIQUE (UAL)

Unité de commande (UC ou unité de contrôle)

=>L’UC est un organe chargé de coordonner le fonctionnement des mémoires, de l’UAL et des organes d’accès pour assurer l’exécution des instructions successives d’un programme. Elle comporte :

- Un registre appelé compteur ordinal qui tient à jour les adresses mémoire des instructions successives à exécuter ; il est commandé par les impulsions d’horloge.

- Un registre d’instruction qui mémorise l’instruction en cours d’exécution.

- Un décodeur d’instruction qui reconnait l’instruction contenue dans le registre instruction (il indique au séquenceur la séquence de micro-commandes à réaliser pour exécuter l’instruction).

- Un séquenceur qui fournit la suite de micro-commandes (chargement, décalage,…) nécessaires au déroulement de l’instruction. Les micro-commandes sont délivrées suivant le rythme de l’horloge interne.

=>Unité Aritmétique et logique (UAL) aussi appelée unité de calcul, UT (Unité de Traitement) ou ALU (Arithmetic and Logical Unit).

L’UAL est un organe dans lequel est effectivement réalisé le traitement des données :

- Opérations arithmétiques : addition, soustraction, décalage droite/gauche, incrémentation, décrémentation.

- Opérations logiques : ET booléen, OU booléen, complémentation, OU exclusif.

- Positionnement d’indicateurs du registre d’état.

L’UAL ne traite que les nombres entiers, les nombres réels sont traités par plusieurs instructions manipulant des entiers. L’UAL reçoit les informations à traiter dans des registres d’entrée et renvoie les résultats à partir d’un registre de sortie. L’accumulateur est un registre qui contient à la fois le premier opérande et reçoit le résultat. Les échanges d’informations entre registres d’entrée/sortie et le reste de l’ordinateur sont déclenchés par l’Unité de Commande.

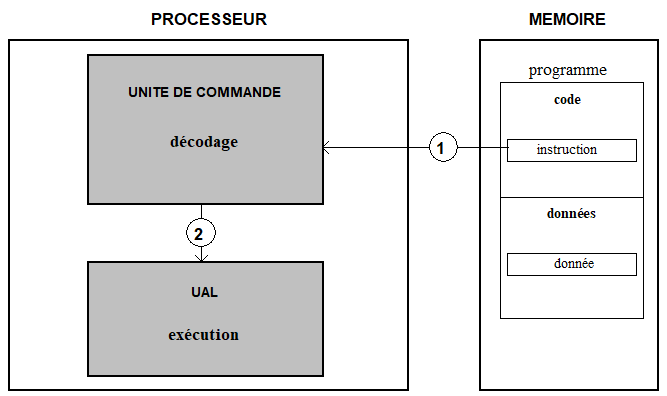

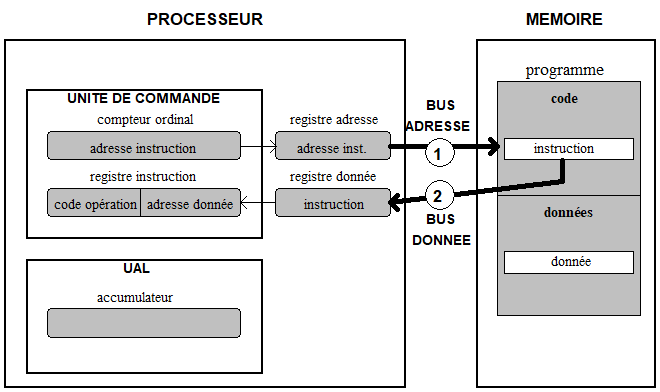

PRINCIPE SIMPLIFIE D’EXECUTION D’UNE INSTRUCTION

EXECUTION D’UNE INSTRUCTION PORTANT SUR UN OPERANDE MEMOIRE

Une instruction processeur est en général composée de deux parties : le code opération qui indique la nature de l’opération à effectuer, et l’adresse de la donnée (ou opérande) qui est la quantité sur laquelle l’opération doit être effectuée.

=>1ère phase : recherche et décodage de l’instruction (cette première phase est valable pour tout type d’instruction).

- Le contenu du compteur ordinal (adresse de l’instruction à exécuter) est envoyé dans le registre d’adresse. Un signal de lecture est envoyé à la mémoire via le bus de commande.

- L’instruction lue est envoyée dans le registre de données, puis transférée dans le registre d’instruction. L’UC décode l’instruction et envoie un ordre de préparation à l’UAL. Le compteur ordinal est incrémenté afin de pointer sur l’instruction suivante.

=> 2ème partie : exécution de l’instruction.

- 3. L’adresse de la zone (contenue dans le registre d’instruction) est envoyée dans le registre adresse (l’UC recherche l’opérande de l’instruction).

- 4. L’UC déclenche le transfert des données à traiter vers l’UAL (registre donnée) qui effectue le traitement. Le résultat est inscrit dans l’accumulateur. L’UC range le résultat en mémoire centrale à l’adresse contenue dans le registre d’instruction (en passant par les registres adresse et donnée).

EXECUTION D’UNE INSTRUCTION DE RUPTURE DE SEQUENCE

Ce type d’instruction, également appelée instruction de branchement ou de saut , permet de modifier le déroulement séquentiel du programme, en faisant suivre l’instruction de rupture de séquence non par l’instruction placée à l’adresse suivante, mais par une instruction dont l’adresse est fournie par l’instruction de rupture de séquence.

Le branchement peut être conditionnel ; il ne sera alors effectif que si une condition, portant généralement sur le contenu de l’accumulateur, est réalisée ; sinon le programme se continuera en séquence.

ARCHITECTURES DES PROCESSEURS POUR MICRO-ORDINATEURS

COMPATIBLES PC

Intel (80×86) a été le seul fournisseur de microprocesseurs pour compatibles PC et PS/2 jusqu’à la fin des années 80. Il reste aujourd’hui le premier fabriquant de microprocesseurs du monde, mais il est concurrencés par plusieurs sociétés produisants des processeurs compatibles Intel : AMD (Advanced Micro Devices), Cyrix (Nippon Electric Compagny), C&T (Chips & Technologies), IBM, Nexgen, …

Historique des principaux processeurs Intel :

|

processeur |

date registre |

bus de |

bus |

copro. |

cache |

cache |

vitesse |

faible |

|

|

(bits) |

données |

d’adresse |

inté- |

intégré |

intégré |

interne |

conso. |

||

|

8088 |

(bits) |

(bits) |

gré |

niveau 1 niveau 2 |

augmentée |

||||

|

1979 |

16 |

8 |

20 |

||||||

|

8086 |

1978 |

16 |

16 |

20 |

|||||

|

80286 |

1982 |

16 |

16 |

24 |

|||||

|

386SX |

1988 |

32 |

16 |

24 |

|||||

|

386SL |

1990 |

32 |

16 |

24 |

oui |

||||

|

386DX |

1985 |

32 |

32 |

32 |

|||||

|

486SX |

1991 |

32 |

32 |

32 |

8 Ko |

||||

|

486SL |

1992 |

32 |

32 |

32 |

8 Ko |

oui |

|||

|

486SX2 |

1994 |

32 |

32 |

32 |

8 Ko |

x 2 |

|||

|

486DX |

1989 |

32 |

32 |

32 |

oui |

8 Ko |

|||

|

486DX2 |

1992 |

32 |

32 |

32 |

oui |

8 Ko |

x 2 |

||

|

Intel DX4 |

1994 |

32 |

32 |

32 |

oui |

16 Ko |

x 3 |

||

|

Pentium |

1993 |

32 |

64 |

32 |

oui |

2 x 8 Ko |

x n |

||

|

Pentium Pro |

1995 |

32 |

64 |

32 |

oui |

2 x 8 Ko |

256 ou |

x n |

|

|

MMX |

1997 |

32 (64) |

64 |

32 |

oui |

2×16 Ko |

512 Ko |

x n |

|

|

Klamath |

1997 |

32 (64) |

64 |

32 |

oui |

x n |

|||

|

Au 1er janvier 1997, les processeurs du marché des compatibles PC sont les suivants : |

|||||||||

|

entrée de gamme |

: Pentium/133 |

||||||||

|

milieu de gamme |

: Pentium/150, 166 |

||||||||

|

haut de gamme |

: Pentium/200 et Pentium Pro 180, 200 |

||||||||

Compatibilité ascendante :

Un microprocesseur de la famille 80×86 est entièrement compatible avec tous les logiciels écrits pour les versions antérieures (par exemple, un logiciel écrit pour un 8086 « tourne » sur un 80386). Tous les processeurs Intel sont basés sur le jeu d’instructions du 8086, avec des enrichissements progressifs en fonction de l’évolution dans la gamme (286, 386, 486, Pentium), mais au fil des générations le code exécutable a acquis de nouvelles instructions. Ainsi, le mode 386 étendu de Windows 3.1 fonctionne uniquement sur les ordinateurs architecturés autour d’un processeur à partir du 80386 (parce que ce logiciel exploite des commandes correspondant à un mode de fonctionnement qui n’existait pas dans le jeu d’instructions du 80286).

VARIANTES D’ARCHITECTURE

=>Coprocesseur intégré : à partir du 486

Un coprocesseur est un dispositif qui étend le jeu d’instructions et le jeu de registres d’un processeur.

Contrairement à l’ALU, un coprocesseur arithmétique, appelé aussi processeur mathématique, FPU (Floating Point Unit), NDP (Numeric Data Processor) ou NPX (Numeric Processor eXtension), travaille directement sur des nombres réels (codification virgule flottante). Pour cela, il dispose, en plus des 4 opérations de base, de nombreuses fonctions mathématiques (trigonométriques, logarithmiques,…). Le coprocesseur arithmétique accélère donc surtout les logiciels ayant recours au calcul réel, tels que DAO, CAO, simulation, synthèse d’image, calcul scientifique, statistiques, tableur, grapheur et PAO.

Sur les anciens PC, un emplacement est réservé au coprocesseur arithmétique externe près du microprocesseur. Mais les nouveaux microprocesseurs, à partir de 486DX, intègrent directement un coprocesseur interne sur la même puce.

=>Cache intégré (noté « C » pour certains processeurs) : à partir du 486

La tendance est à l’intégration d’un cache (dit de « 1er niveau ») de plus en plus grand à l’intérieur même du processeur, ce qui n’exclue pas un cache processeur extérieur (dit de 2ème niveau). Le Pentium Pro intègre même ce cache de second niveau à l’intérieur du processeur.

=>Processeurs DX et SX.

Le terme « SX » désigne une version simplifiée d’un processeur « DX ». Mais, suivant les processeurs, cette simplification n’est pas de même nature.

Un 386SX est un 386 avec un bus de données de 16 bits (au lieu de 32 bits pour le DX).

Un 486SX est un 486 sur lequel on a inhibé le coprocesseur (l’architecture restant 32 bits).

=>Augmentation de la vitesse interne (noté avec un chiffre multiplicateur pour certains processeurs tels que le 486 DX2).

Le processeur peut être caractérisé par deux fréquences au lieu d’une : la fréquence interne et la fréquence de la carte mère d’accueil (actuellement, 66 MHz maximum). Ainsi, le processeur peut fonctionner en interne à une certaine fréquence, et communiquer avec l’extérieur à une autre fréquence moins élevée.

Le multiplicateur de fréquence est un composant placé au niveau de l’interface avec le bus externe. On obtient ainsi une machine moins chère et rapide sur le plan des traitements au détriment des seules entrées/sorties.

|

coefficient |

processeur |

fréquence interne |

fréquence externe |

|

x 1.5 |

Pentium/100 |

100 |

66 |

|

x 2 |

Pentium/133 |

133 |

66 |

|

x 2.5 |

Pentium/150 |

150 |

60 |

|

x 3 |

Pentium/166 |

166 |

66 |

|

Pentium/180 |

180 |

60 |

|

|

Pentium/200 |

200 |

66 |

|

|

Pentium Pro/180 |

180 |

60 |

|

|

Pentium Pro/200 |

200 |

66 |

=>Economie d’énergie (notée L pour Low power)

Certains processeurs sont équipés d’une unité de gestion de la consommation, et fonctionnent à une tension interne moindre, afin d’être utilisés pour les portables. Ce type de processeur est statique, c’est-à-dire que, même sans être alimenté pendant une durée assez longue, il conserve son état courant (les autres processeurs ont besoin d’être régulièrement « rafraîchis » pour continuer à fonctionner).

Exemples : 386SL, 486SL et Pentium VRT (Voltage Reduction Technology) d’Intel.

=>Evolution des PC

Plusieurs solutions sont possibles afin de « doper » un micro- ordinateur : échange de processeur (pour un processeur de même brochage, et une carte mère ayant un processeur extractible), ajout d’un overdrive (pour une carte mère ayant un support overdrive) ou changement de carte mère.

MACINTOSH

Motorola (68xxx) est le processeur de base du Macintosh d’Apple. Aujourd’hui, les derniers Macintosh tendent à s’équiper de processeur Risc PowerPC codéveloppé par IBM, Apple et Motorola.

JEU D’INSTRUCTIONS DU PROCESSEUR

JEU D’INSTRUCTIONS

Un processeur exécute des ordres écrits en langage machine. Dans ce langage, chaque instruction élémentaire est représentée par un code particulier, exprimé sur un ou plusieurs octets (ce code spécifie notamment le traitement à effectuer et les opérandes concernées : registres, mémoire, mode d’adressage,…).

Le jeu d’instructions d’un processeur particulier est donc constitué par l’ensemble des codes qu’il est capable de reconnaître et d’exécuter. Par exemple,…

=>Instructions de traitement :

- Transfert entre mémoire et registre, ou entre registres (MOV (transfert), PUSH et POP (empiler/dépiler)).

- Opérations arithmétiques sur les nombres entiers (ADD, SUB, MUL, DIV,..).

- Opérations arithmétiques en virgule flottante.

- Instructions logiques (NOT, AND, OR,…).

- Instructions de décalage.

=>Instructions de branchements (CALL, RET, JMP,…).

=>Instructions d’entrée/sortie : envoi et demande de données avec les ports (IN, OUT).

=>Instructions de commande et d’état : commande la mise d’un organe de la machine dans un certain état, ou teste l’état dans lequel se trouve cet organe.

REALISATION DU SEQUENCEUR DE L’UNITE DE COMMANDE

Chaque instruction élémentaire correspond à un circuit câblé ou à un micro-programme.

=>Logique câblée (logique discrète)

Toutes les fonctions (transformation des bits) sont représentées par des circuits reliés électriquement entre eux. Cette solution permet d’obtenir des fonctions (additionneurs, multiplicateurs, décaleurs de bits,…) qui ne réclament qu’un seul cycle d’horloge.

Inconvénient de la logique câblée : il faut autant de circuits que de fonctions et, quand le processeur doit offrir un grand nombre de fonctions, le câblage d’interconnexion des circuits devient inextricable, ce qui rend le coût de développement et le risque d’erreur élevés.

=>Logique micro-programmée (logique séquentielle, microprogrammation)

Il n’est donc pas possible pour la plupart des microprocesseurs « classiques » (dits CISC) de câbler directement les actions à exécuter pour chaque instruction de leur langage machine (celles-ci sont trop nombreuses et effectuent parfois des traitements complexes). L’exécution d’une instruction est donc décomposée en étapes élémentaires, qui sont, quant à elles, exécutées par des blocs de logique câblée.

Le microcode est la manière de programmer chaque instruction en fonction des éléments de base (câblés) disponibles. Les circuits accomplissent diverses opérations selon les instructions de ce microcode. Le microcode est appelé firmware (intermédiaire entre software et hardware) et est stocké dans la ROM de commande de l’Unité de Commande du processeur. Le code opération de l’instruction

- exécuter est considéré comme l’adresse dans la mémoire de commande de la première micro-instruction du microprogramme associé à l’instruction.

Cette technique d’ajout d’instructions complexes, sous forme de microprogrammes composés par une suite d’opérations élémentaires, s’appelle la microprogrammation.

Avantages de la logique micro-programmée : réduction du coût de réalisation, facilité de test du séquenceur et d’ajout d’instructions (plus facile dans une ROM que de modifier un séquenceur câblé).

Inconvénients de la logique micro-programmée : cette méthode nécessite d’implanter sur les puces des ROM qui pénalisent les performances en raison du temps nécessaire au décodage et au séquencement des instructions. De plus, chaque étape élémentaire d’une instruction nécessite un cycle d’horloge ; une fonction standard ne peut donc pas se réaliser en moins de 3 à 10 cycles (et certaines instructions complexes nécessitent plusieurs dizaines de cycles).

=>Logique utilisée par les processeurs actuels

- Le 80386 est entièrement à base de microcode.

- A partir du 486, les processeurs Intel sont réalisés avec un mélange des deux logiques. La logique câblée concerne les instructions les plus fréquemment utilisées, la majeure partie des fonctions restant sous forme de microcode. On obtient un compromis entre performance (logique câblée) et coût de développement acceptable (logique micro-programmée).

- Les processeurs RISC sont basés sur la logique câblée, ils ne proposent pas d’instructions complexes, celles-ci doivent donc être prises en charge par les compilateurs.

ARCHITECTURES EVOLUEES

ARCHITECTURES CISC ET RISC

=>CISC (Complex Instructions Set Computer)= processeur à jeu d’instructions classique tels que ceux utilisés sur les micro-ordinateurs (Intel 386, Motorola 68030,…).

Il s’agit de processeurs complexes comportant beaucoup d’instructions (plusieurs centaines, car la volonté d’assurer la compatibilité d’un modèle à l’autre a conduit les constructeurs à garder, dans chaque nouvelle machine, des instructions fossiles). Certaines instructions sont complexes avec une grande variété de formats différents (car au début de l’informatique une grande partie des développements se faisait en assembleur).

Le jeu d’instructions est donc le plus complet possible (plusieurs centaines d’instructions), ce qui implique une complexité du microcode (jeu d’instructions) et des programmes pas forcément très performants (une instruction complexe peut être plus lente que son équivalent en succession d’instructions simples), le temps d’exécution d’une instruction allant de 2 à 12 cycles. De plus, la plupart des instructions microcodées sont pas, ou peu, utilisées ; les instructions générées par les compilateurs sont, dans 50% à 70% des cas, du type LOAD, CALL et BRANCH.

L’efficacité d’une machine n’est donc pas forcément liée à la diversité du jeu d’instructions.

=>RISC (Reduced Instructions Set Computer) = processeur à jeu réduit d’instructions tels que ceux utilisés sur les stations de travail (Alpha de DEC, Power d’IBM, Sparc de Sun, PA8000 de HP, R8000 de Mips,…).

Il s’agit de processeurs utilisant une logique câblée (pas de microcode), un grand nombre de registres (plusieurs centaines) et des pipelines (commencement de l’exécution d’une instruction avant même que la précédente ne soit achevée).

Le jeu d’instructions est réduit à une cinquantaine avec peu d’instructions avec référence mémoire, exécution de la plupart des instructions en un seul cycle machine, des instructions courtes (un seul accès mémoire permet alors de charger plusieurs instructions) et de formats homogènes (afin de simplifier et d’accélérer le décodage).

|

technologie |

CISC |

RISC |

|

instructions |

complexes, prenant plusieurs cycles |

simples, ne prenant qu’un cycle |

|

séquenceur |

microprogrammé |

câblé |

|

localisation de la complexité |

dans le microprogramme |

dans le compilateur |

|

format des instructions |

variable |

fixe |

|

nombre d’instructions et de modes d’adressage |

beaucoup |

peu |

|

nombre de registres |

peu |

beaucoup |

|

instructions avec référence mémoire |

toutes les instructions peuvent faire |

seules deux instructions font accès |

|

des accès à la mémoire |

à la mémoire (lecture/écriture) |

Ces deux technologies tendent à fusionner car les derniers processeurs CISC (à partir du 486 d’Intel) s’inspirent du RISC (pipeline, exécution des instructions les plus fréquentes en un cycle d’horloge). De même, le terme RISC ne veut plus dire grand chose et on ne le conserve que par habitude. Par exemple, l’Alpha 21064 de DEC comprend 168 instructions et le Power PC 601 près de 200, alors que le pentium n’en a que 220. Enfin, le Pentium Pro transforme chaque commande en une série d’instructions élémentaires de type RISC appelées micro-ops.

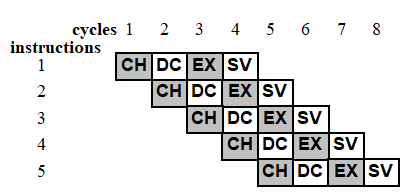

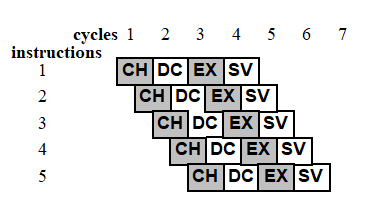

ARCHITECTURE PIPELINE : pour exécuter une instruction par cycle (en moyenne)

=>Pipeline

Le traitement d’une instruction nécessite plusieurs phases, par exemple :

| CH | chargement (lecture) de l’instruction |

| DC | décodage de l’instruction (et sélection des registres et/ou des adresses d’entrée/sortie) |

| EX | exécution proprement dit |

| SV | sauvegarde (écriture) du résultat en mémoire |

Une architecture pipeline consiste à segmenter les unités qui accomplissent ces tâches afin de pouvoir commencer une nouvelle instruction alors que la précédente n’est pas terminée (c’est le travail à la chaîne du processeur). Ainsi, une 1ère instruction peut en être au stade de l’exécution, pendant qu’une 2ème en est au décodage et qu’une 3ème est en cours de chargement. En fait, la réalité est un peu plus compliquée dans la mesure ou le temps exigé pour une étape donnée n’est pas toujours le même pour toutes les instructions.

Le nom « pipeline » a été donné par analogie avec les canalisations où le carburant liquide entre, s’écoule et ressort.

Les pipelines sont apparues dans les première générations de supercalculateurs (Cray 1, IBM 360/91, Control Data 6600, Cyber) et se rencontre aujourd’hui sur la plupart des minis (Vax,…) et micros (486 avec pipeline simple, Pentium avec pipeline double).

=>Super-pipeline

La technique de superpipeline améliore le pipeline en découpant chacune des étapes en n niveaux intermédiaires avec mémorisation (on parle de superpipeline au delà de 4 niveaux).

Exemples : R4000, Pentium (2 pipelines de 5 niveaux), Pentium Pro (14 niveaux), Motorola 68040 (pipeline de 6 niveaux).

=>Problèmes du pipeline

La présence d’un pipeline conduit à minimiser le nombre de sauts et de branchements conditionnels dans les programmes. En effet, il faut repipeliniser à partir de la nouvelle adresse et donc attendre un ou plusieurs cycles d’horloge avant de reprendre le rythme normal d’exécution (le nombre de branchements est en moyenne de 1 pour 6 à 9 instructions).

=>Améliorations du pipeline :

-

- La technique de prédiction de branchement consiste à détecter la présence d’un saut avec un cycle d’avance, et donc à pipeliniser l’instruction qui sera effectivement exécutée le cycle suivant (en cas d’erreur, le pipeline est purgé).

Exemples : 88110 et Power PC de Motorola, Pentium et Pentium Pro d’Intel (mais pas le 486), Alpha de DEC.

- La technique d’exécution spéculative consiste à exécuter par anticipation l’instruction qui se trouve à l’adresse suivante et à ne pas sortir le résultat s’il fallait la sauter.

Exemples : Pentium Pro d’Intel (mais pas le Pentium), 29000 d’AMD.

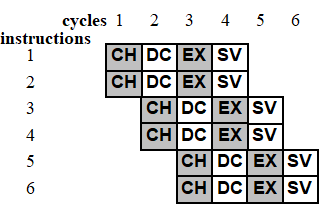

ARCHITECTURE SUPERSCALAIRE : pour exécuter plusieurs instructions par cycle

=>Un processeur superscalaire incorpore plusieurs Unité de Traitement (ALU). A chaque cycle d’horloge, le processeur peut donc exécuter autant d’instructions qu’il contient d’ALU.

=>Cette architecture permet d’exécuter plusieurs instructions par cycle …

mais il y a les processeurs qui permettent d’exécuter plusieurs instructions de même type par cycle (2 instructions entières par cycle pour le Pentium, et 3 pour le Pentium Pro), …

et ceux qui permettent seulement d’exécuter plusieurs instructions de types différents par cycle (le Power 1, le Power PC et l’Alpha exécutent jusqu’à 4 instructions par cycle : entère, flottante, branchement et condition ; Le Power 2 exécute 6 instructions par cycle).

=>La complexité de cette architecture vient de la gestion de l’unité de traitements et des registres, ainsi que de l’organisation du code pour optimiser le parallélisme.

En effet, deux instructions consécutives devant être exécutées par la même ALU ne pourront être parallélisées. De plus, une instruction devant utiliser le résultat d’une opération précédente pourra être parallélisée mais sera suspendue tant que le résultat attendu ne sera pas disponible.

Une unité de présélection des instructions permet de détecter les informations indépendantes et de leur faire suivre un chemin compatible avec l’ordre logique de délivrance des résultats. Pour ne pas ralentir le processeur, cette unité de présélection doit puiser ses informations au sein d’un cache.

Le Pentium Pro a adopté l’exécution dans le désordre. Les instructions demandant un accès mémoire pour lire des données sont placées en attente, tandis que d’autres instructions sont traitées. En sortie de calcul, un dispositif replace les résultats dans le bon ordre.

Un compilateur spécifique est indispensable pour optimiser ce type de processeur ; il doit être capable de réorganiser l’ordre des instructions pour éviter les cycles d’attente.

TECHNOLOGIE MMX (MultiMedia eXtension) d’Intel : Pentium multimédia (début 97).

Un processeur MMX est doté d’un jeu de 57 instructions supplémentaires permettant d’exécuter plus rapidement les opérations les plus utilisées en multimédia. De plus, un tel processeur offre un traitement parallèle des données (calcul vectoriel SIMD : Single Instruction – Multiple Data).

Comme pour les coprocesseur, pour qu’une application bénéficie de ce gain de performances, il faut qu’elle ait été prévue pour. La cible des Pentium MMX semble être d’abord le marché grand public.

Exemples : MMX (Pentium MMX/ 166 et 200), Klamath (Pentium Pro MMX/233 et 266) d’Intel.

VLIW (Very Long Instruction Word) : instructions très longues

En VLIW, les instructions sont suffisamment longues pour contenir des opérations multiples. Un processeur VLIW est donc forcément un processeur superscalaire.

Les instructions sont en fait découpées en n opérations élémentaires associées chacune à une unité de traitement. La logique de décodage des instructions est réduite à sa plus simple expression car l’affectation des opérations aux unités de traitement est déjà codée dans l’instruction elle-même. De plus, le processeur n’a pas à gérer les conflits de ressources et d’utilisation des registres (c’est le compilateur qui structure le code en conséquence).

Exemples : i860 d’Intel, futur P7 d’Intel/HP (jusqu’à 30 instructions Risc par cycle).

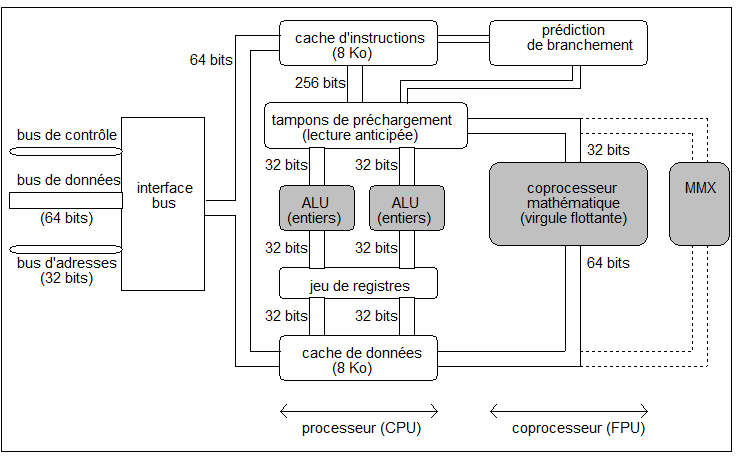

EXEMPLE DU PENTIUM

Le Pentium a une architecture mi 32 mi 64 bits :

ALU et bus interne de données 32 bits bus de données externe 64 bits FPU 80 bits

registre de décodage d’instruction et cache d’instructions256 bits

Le Pentium a une architecture CRISC (Complex Reduced Instruction Set Computer), c’est-à-dire qu’il est apparenté aux CISC et aux RISC. Il dispose notamment …

-

- d’un câblage des instructions les plus fréquemment utilisées,

- d’un coprocesseur arithmétique utilisant des instructions câblées, donc plus rapide que celui du 486 (qui utilise des instructions sous forme de microcode),

- d’un double pipeline avec unité de prédiction de branchement,

- d’une architecture superscalaire. Le Pentium comprend l’équivalent de deux 486 oeuvrant en parallèle ; une unité de contrôle se charge de répartir les diverses instructions entre les deux 486, suivant leur disponibilité (pour les instructions d’une même tâche, mais il n’y a pas répartition de tâches distinctes) ; ce qui permet d’exécuter jusqu’à 2 instructions par cycle d’horloge.

TECHNOLOGIE DES MICROPROCESSEURS

NIVEAUX D’INTEGRATION

La cellule de base de tout processeur est le transistor. Ce composant fondamental de l’électronique numérique agit comme un micro-interrupteur laissant ou non passer le courant selon le voltage qui lui est appliqué. L’association de plusieurs milliers de transistors au sein de structures complexes réalise les fonctions souhaitées par les concepteurs du circuit intégré (registres, décodeur d’instructions, unité arithmétique et logique, bus interne, adressage de la mémoire,…).

La fabrication du microprocesseur est le résultat du transfert d’un schéma électrique sur une plaquette de silicium. Ce schéma possède plusieurs couches superposées sur une seule plaquette pour former le circuit final. Ce circuit est enfermé dans un boîtier en céramique ou en plastique, puis relié aux broches pour former un microprocesseur.

L’augmentation de la fréquence des microprocesseurs accroît la température de fonctionnement. Pour limiter cet effet, on peut :

équiper le processeur d’appareils de refroidissement,

ou augmenter l’intégration qui se mesure à l’écartement (exprimé en microns) entre deux composants élémentaires sur une puce (la tension d’alimentation décroît avec la finesse de la gravure).

|

technologie |

tension d’alimentation |

processeur |

|

0,8 micron |

5 V |

486 DX2/66 et Pentium/60, 66 |

|

0,6 micron |

3,3 V |

DX4, Pentium/75, 90 et 100 et Pentium Pro/150 |

|

0,35 micron |

2,9 V |

Pentium/120, Pentium Pro/166, 180 et 200, MMX, Power PC 604e |

|

0,18 à 0,28 |

Klamath |

Pour la technologie 0.8 micron, à haute fréquence (60 MHz), la dissipation thermique considérable (jusqu’

- 16 Watts) nécessite un refroidissement par un gros radiateur et un ventilateur. Les premiers Pentium (60 et 66) présentaient de tels problèmes de surchauffe (75°C) que les concurrents d’Intel les ont surnommés les barbecues. Pour la technologie 0.6 microns, la consommation (4 Watts) se contente d’un simple radiateur.

TECHNOLOGIE DES PROCESSEURS

Les processeurs des grands systèmes utilisent la technologie bipolaire (ou ECL : Emitter Coupled Logic).

Les microprocesseurs quant à eux utilisent une technologie dite CMOS (Complementary Metal Oxyde Semiconductor). Les processeurs CMOS sont moins puissants (23 Mips contre 60 Mips), mais plus simple

- frabriquer (donc moins chers à l’achat) que les processeurs bipolaires. Cependant, l’écart entre ces deux types de processeurs devrait résorber rapidement compte tenu de la progression des performances du CMOS. De plus, la technologie CMOS, consommant moins de courant et dégageant moins de chaleur, nécessite un équipement de refroidissement moins important permettant donc d’obtenir une architecture plus compacte. Les grands systèmes commencent à utiliser cette technologie CMOS.

MODES DE FONCTIONNEMENT DES PROCESSEURS INTEL

MODE REEL (mode du 8086 et de MS/DOS)

Le microprocesseur se comporte comme un 8086 classique, mais il connaît alors la même limitation d’adressage mémoire. Les segments et les registres d’adressage sont utilisés de la même façon que pour le 8086 afin d’accéder à 1 Mo de RAM. Ce mode assure la compatibilité avec les logiciels écrits sur un PC équipé d’un 8086 et portés sur un processeur des générations suivantes.

Avec ce mode, un programme peut aller écrire à un endroit quelconque de la mémoire ou prendre librement le contrôle d’un périphérique. Mais, ce qui convenait pour le monotâche, n’est plus adapté pour le multitâche (où un programme peut modifier accidentellement un autre programme en mémoire ou ses données).

MS/DOS ne sait utiliser que ce mode sur un 80×86 et suivants.

MODE PROTEGE (mode apparu à partir du 80286) = mode standard de Windows

Le mode protégé améliore la gestion mémoire en permettant l’adressage direct de 16 Mo de mémoire sur un 80286, et 4 Go à partir du 486. A partir du 80286, un mécanisme de protection de la mémoire (gravée dans le silicium du microprocesseur) supprime le risque de collision entre programmes quand on travail en mode protégé. De plus, ce mode permet la gestion de mémoire virtuelle (4 Go sur le 80286, 64 To sur le 80386). Une interruption prévient le système lorsqu’une tâche a besoin d’un segment de mémoire non résident ; il échange alors une portion de mémoire non utilisée avec le segment demandé.

Ce mode offre également un fonctionnement multitâche. Chaque tâche dispose de sa propre table de description indiquant les segments qu’elle utilise. Dans un contexte multitâche, lorsque le processeur commute sur une autre tâche, il n’a besoin de stocker que cette table de description et le contenu des registres. Chaque tâche ayant sa table de description, elle ne peut utiliser les segments qui ne lui appartiennent pas.

Systèmes utilisant ce mode : Windows (mode standard), OS/2, UNIX,…

MODE 86 VIRTUEL (mode intermédiaire apparu avec le 80386)

La différence entre le mode 8086 virtuel et le mode réel (qui lui aussi émule un 8086) est qu’il peut y avoir plusieurs environnements 8086 virtuels en même temps. Le microprocesseur peut réaliser plusieurs tâches indépendantes entre elles, en simulant l’exécution de plusieurs 8086 dotés chacun de leur propre mémoire. Le processeur 386 est capable de gérer des segments de mémoire pouvant atteindre 1 Mo ; les programmes qui s’exécutent dans ces segments fonctionnent exactement comme dans la mémoire d’un compatible IBM PC (8086/88), chacun de ces segments est appelé machine virtuelle MS/DOS.

Ce mode utilise la pagination (pages de 4 Ko) : pour que les adresses des différentes sessions 8086 virtuelles ne se mélangent pas dans la mémoire physique, le 80386 crée des adresses linéaires en ajoutant les contenus des registres de segment et de déplacement. Une table transforme ensuite cette adresse linéaire en adresse physique.

EXERCICES

* Vous voulez « doper » votre PC, quelles solutions s’offrent à vous dans les différents cas suivants ?

- Vous avez un Pentium/133 avec 16 Mo de RAM.

- Vous avez un 486 DX2.

- Vous avez un 386 SX.

* Quelle différence existe-t-il entre un POP (Pentium Overdrive Processor) et un Pentium ?

* Sur quel type de processeur sont basés les Macintosh ?

* Quel type de processeur utilise-t-on sur les stations de travail ? Citer 3 processeurs ce type.

* Quels sont les rôles respectifs des organes ALU, FPU et MMX du microprocesseur.

* Est-ce qu’un compatible PC a forcément un microprocesseur de marque Intel.

* Qu’a de particulier un microprocesseur par rapport aux autres processeurs ?

- Est-ce qu’un micro-ordinateur est forcément équipé d’un microprocesseur ?

- Qu’est-ce que la loi de Moore ?

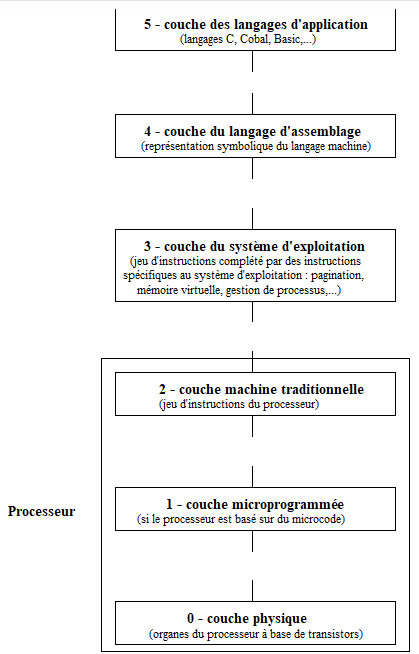

*Complétez le schéma suivant en indiquant entre chaque couche le type d’action à réaliser.