1. Les différents types de supports physiques

Il y a plusieurs manières d’intégrer physiquement des puces RAM à la carte mère ou à la carte d’extension. Les systèmes anciens utilisent des puces mémoire séparées, appelées des puces DIP (à doubles rangées de broches), qui étaient raccordées par des connecteurs ou soudées directement à une carte.

La plupart des systèmes modernes utilisent des barrettes mémoires appelées SIMM (Single In-line Memory Module = module mémoire à simple rangée de broches de connexion).

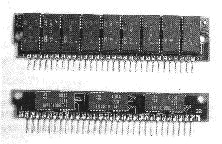

Ce type de module combine plusieurs puces sur une petite plaquette enclenchée dans un socle de maintien. Le module SIPP est semblable à un SIMM, mais utilise des broches à la place du connecteur plat pour se connecter à la carte mère. Il est possible de transformer une barrette SIPP en SIMM en supprimant les broches, ou de transformer une SIMM en SIPP en soudant les broches. Certaines sociétés fabriquent des convertisseurs de SIPP en SIMM qui permettent au SIPP de se brancher sur des connecteurs SIMM 30 broches conventionnels. Il existe donc actuellement 4 types de support de mémoire. Les puce DIP, les barrettes SIPP, SIMM et DIMM. Une nouvelle génération de mémoires, la RDRAM, devraient se généraliser en 1999.

Ce type de module combine plusieurs puces sur une petite plaquette enclenchée dans un socle de maintien. Le module SIPP est semblable à un SIMM, mais utilise des broches à la place du connecteur plat pour se connecter à la carte mère. Il est possible de transformer une barrette SIPP en SIMM en supprimant les broches, ou de transformer une SIMM en SIPP en soudant les broches. Certaines sociétés fabriquent des convertisseurs de SIPP en SIMM qui permettent au SIPP de se brancher sur des connecteurs SIMM 30 broches conventionnels. Il existe donc actuellement 4 types de support de mémoire. Les puce DIP, les barrettes SIPP, SIMM et DIMM. Une nouvelle génération de mémoires, la RDRAM, devraient se généraliser en 1999.

Fig. 1: Des barrettes SIP, avec leurs fines pattes soudées sont presque aussi délicates à installer que les puces traditionnelles

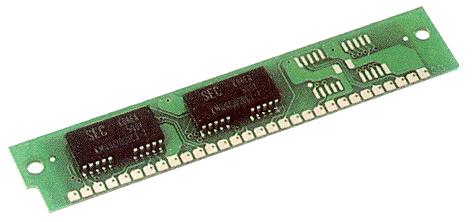

1.1 Format d’une barrette SIMM 8 bit.

Fig. 2: Les barrettes SIMM 30 broches sont plus pratiques. L’échancrure à gauche évite qu’elles soient montées à l’envers. Ce sont des barrettes 8 bits.

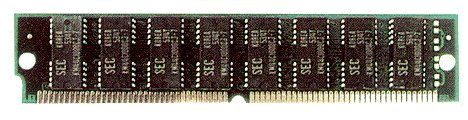

1.2 Format d’uns barrette SIMM 32 bit

|

Barrette SIMM 72 broches 32 bits |

Montage d’une barrette SIMM 72 broches |

|

fig A |

Fig B |

|

L’échancrure au milieu et à gauche évite qu’elle soit montée à l’envers. |

Fig A

Fig B

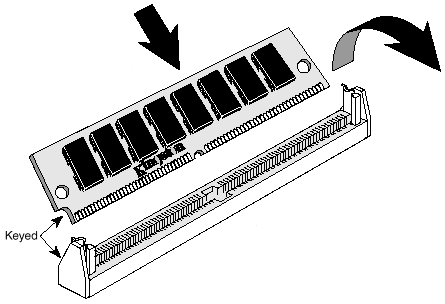

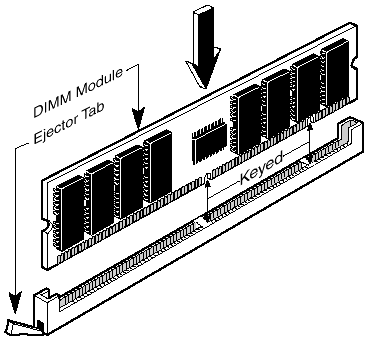

1.3 Format d’uns barrette DIMM 64 bit

|

Barrette DIMM 168 broches en 64 bits. |

Montage d’une barrette DIMM 168 broches |

|

Fig A |

Fig B |

|

Les deux échancrures au milieu évitent de monter la barrette à l’envers. Ces barrettes existent en 3,3 v et en 5 v. La position des échancrures varie en fonction de la tension de la barrette. |

Fig A

Fig B

1.4 Format de la barrette RDRAM

Ce sont des barrettes mémoires séries constituées de composants 16 bits ( ou 18 bits ) avec un connecteur de 184 broches. On a donc une largeur de bus de 16 bits ( Oui j’ai bien dit 16 bits ). Ce type de mémoire devrait faire son apparition début 1999.

2. Bancs de mémoire

Les barrettes mémoire ( SIPP, SIMM et DIMM ) sont organisées en bancs sur les cartes mères et les cartes mémoires. Vous devez connaître l’agencement du banc de mémoire et sa position sur les cartes mères et les cartes mémoires quand vous ajoutez de la mémoire au système. En outre, les diagnostics mémoire indiquent les emplacements des erreurs par octet et par adresse et vous devez utiliser ces chiffres pour savoir où se trouve le banc défectueux. Les bancs de mémoire correspondent, en général, à la capacité du bus de données du microprocesseur.

Le Tableau suivant montre la taille de chaque banc selon le type de PC :

|

Processeur |

Bus de données |

Taille du banc |

SIMM 30 broches par banc |

SIMM 72 broches par banc |

|

8088 |

8 bits |

9 bits |

1 |

1 (4bancs) |

|

8086 |

16 bits |

18 bits |

2 |

1 (2bancs) |

|

286 |

16 bits |

18 bits |

2 |

1 (2bancs) |

|

386SX, SL, SLC |

16 bits |

18 bits |

2 |

1 (2bancs) |

|

386DX |

32 bits |

36 bits |

4 |

1 |

|

486SLC,SLC2 |

16 bits |

18 bits |

2 |

1 (2bancs) |

|

486SX, DX, DX2, DX4 |

32 bits |

36 bits |

4 |

1 |

|

Pentium |

64 bits |

72 bits |

8 |

2 |

Le nombre de bits de chaque banc peut être fait de simples puces ou de SIMM. Par exemple, dans un système 286 utilisant un banc 18 bits, vous pourriez faire un bloc de 18 puces d’une capacité de 1 bit, ou utiliser quatre puces d’une capacité de 4 bits, pour les bits de données, et deux puces d’une capacité de 1 bit comme bits de parité. La plupart des systèmes modernes n’utilisent pas de puces mais des SIMM. Si le système dispose d’un banc 18 bits, il utilisera plutôt des SIMM 30 broches, deux par banc. Toutes les barrettes SIMM d’un même banc doivent être de la même taille et du même type. Comme vous pouvez le constater, les SIMM 30 broches sont moins intéressants pour les systèmes 32 bits parce que vous devez en utiliser quatre par banc !

Ces SIMM n’étant disponibles qu’en 1 Mo ou 4 Mo, cela signifie qu’un banc doit faire 4 Mo ou 16 Mo de mémoire. II n’y a pas de capacité intermédiaire.

L’utilisation de SIMM 30 broches dans un système 32 bits limite artificiellement la configuration de la mémoire et n’est pas conseillé. Sur les systèmes 32 bits qui utilisent des SIMM 72 broches, chaque SIMM représente un banc séparé et peut être ajouté ou enlevé individuellement, et non forcément par groupe de quatre. La configuration de la mémoire est ainsi plus facile et plus souple. Par contre sur des systèmes 64 bits comme les Pentium II, les barrettes SIMM doivent être utilisées par paires. Seules les barrettes DIMM de 64 bits peuvent être montées par unité.

La disposition physique sur les cartes mères ou les cartes mémoire est arbitraire, elle est déterminée par les constructeurs. Vous pouvez choisir la disposition de votre carte mère ou de vos cartes d’extension en faisant des tests, mais cela prend du temps et ce n’est pas toujours facile, surtout si vous avez des problèmes avec votre système. La documentation de votre système ou de votre carte vous y aidera.

2.1 Mémoire avec Parité et sans Parité.

Les mémoires avec parité sont des mémoires qui utilisent 1 bit supplémentaire pour stocker la parité d’un octet ( 8 bits ). C’est à dire que lorsque le système écrit un octet, par exemple 0000 0010, il compte le nombre de bit qui sont à 1. Si ce nombre est pair alors le bit de parité est mis à 0 sinon il est mis à 1. De même, à chaque lecture, le système recalcule le nombre de bit à 1 et vérifie que le résultat correspond bien à la valeur stockée. Pour que le contrôle de parité soit effectué, il faut au préalable qu’il soit activé dans le bios. Lorsqu’une erreur de parité est détectée, le système est toujours arrêté brutalement avec un message du type :

‘PARITY ERROR AT 0AB5:00BE. SYSTEM HALTED.’

Et cela pour les systèmes d’exploitation DOS, Windows v3.11 et Windows 95, car c’est une erreur matérielle classifiée de ‘FATALE’ et que l’on ne peut pas ignorer. Par contre certains systèmes comme Linux ou SCO-Unix, gèrent eux même cette erreur soit en détournant l’interruption 02h soit en mettant à zéro le bit 7 du port 70h. Certain type de mémoire stocke le nombre de bit impair au lieu du nombre de bit pair. Le tableau suivant fournit la valeur du bit de parité en fonction du type de mémoire

|

Type |

Bits de données |

Nombre de 1 |

Bit de parité |

|

Parité pair |

0000 0000 |

pair |

0 |

|

1000 1001 |

impair |

1 |

|

|

Parité impaire |

1000 1000 |

pair |

1 |

|

0111 0000 |

impair |

0 |

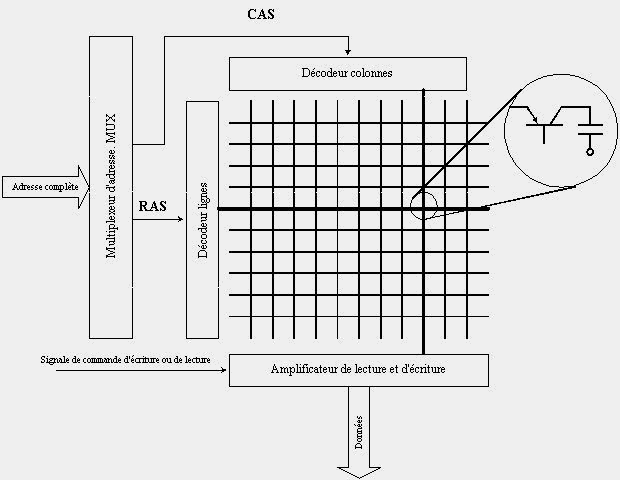

3. Structure physique de la mémoire.

La mémoire est organisée sous la forme d’une grille dont chaque nœud correspond à un transistor. On utilise la capacité résiduelle du transistor pour stocker l’information.

- Le processeur envoie l’adresse complète au multiplexeur / dé multiplexeur de la mémoire, le MUX, et spécifie s’il s’agit d’une lecture ou d’une écriture.

- Le circuit de multiplexage divise l’adresse en deux parties. Les bits de poids fort contiennent l’adresse de la ligne et les bits de poids faibles l’adresse de la colonne. Le signal Row Adress Strob ( RAS ) est généré pour indiquer à la DRAM qu’il s’agit d’une adresse ligne. Puis le signal Column Adress Strob ( CAS ) est généré pour indiquer à la DRAM qu’il s’agit d’une adresse colonne.

- Si une lecture est effectuée alors le bit, situé à l’intersection de la ligne et de la colonne, est envoyé sur la ligne de donnée. Dans le cas contraire la donnée est écrite à la même intersection.

La mémoire est composée de transistors que l’on utilise comme des condensateurs. Afin de compenser les pertes de charge de ces condensateurs la mémoire doit être régulièrement rafraîchie. Pendant le rafraîchissement, il n’y a pas d’accès possible à la mémoire, ni en lecture ni en écriture. Le processeur doit attendre quelques cycles pour que le rafraîchissement soit terminé. Ces temps d’attente, appelé en anglais Waitstates ou Temps de Latence, font chuter les performances du système. On s’efforce donc de les réduire autant que faire se peut. Ils ne sont pas les mêmes pour tous les composants, de sorte qu’il existe des composants de mémoire plus ou moins rapides.

Les temps d’accès s’évaluent en nano secondes et sont compris entre 40 ns et 120 ns. Une nano seconde vaut un milliardième de seconde = 10-9 s ! ). Plus ce temps est long, plus le composant de mémoire est lent.

La vitesse de rafraîchissement ne peut pas s’adapter à la vitesse d’accès des composants de mémoire. Elle est tenue de respecter des limites bien précises imposées par la construction de la carte mère. Pour les cartes mères modernes, on exige en général un temps d’accès de 60 ns , 70 ns ou 80 ns. L’utilisation de composants de mémoire plus lents provoque en général de graves erreurs de lecture alors que des composants plus rapides n’apportent aucun gain de vitesse supplémentaire. Au contraire, les mémoires très rapides, par exemple avec 40 ns de temps d’accès nécessitent éventuellement aussi un rafraîchissement plus rapide et si la carte mère ne le fournit pas en temps voulu, il y a de fortes chances pour que la mémoire ait déjà tout oublié. La perte de performance due aux temps d’attente est très sensible sur les cartes mères modernes cadencées à 100 Mhz et davantage. Pour remédier à ce problème, on utilise deux procédés fondamentalement différents, seuls ou combiné:

Un cache externe de mémoire statique, généralement de 256 Ko.

De nouvelles technologies des mémoires, les RAM EDO, BEDO, SDRAMRDRAM

3.1 Chronogramme des cycles d’accès.

Les boîtiers de mémoire dynamique n’ont pas de commande de validation. Ce rôle est remplit par la conjonction des signaux RAS et CAS. Il y a trois cycles de base pour une mémoire dynamique, le cycle de lecture, le cycle d’écriture et le cycle de rafraîchissement

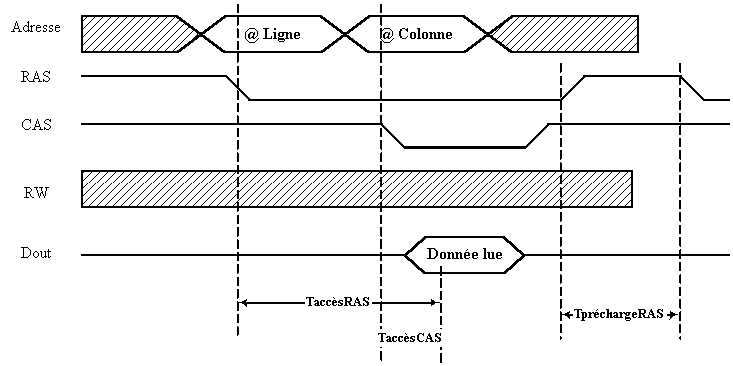

3.2 Cycle de lecture

- TaccèsRAS : C’est le temps d’accès à partir de l’activation du signal RAS. Il s’agit du temps d’accès effectif en lecture.

- TaccèsCAS :C’est le temps d’accès à partir de l’activation du signal CAS.

- TpréchargeCAS :C’est le temps de pré chargement du signal RAS. Après chaque accès il faut garantir une certaine durée d’inactivité ( RAS désactivé ) avant de pouvoir commencer un nouveau cycle ( par exemple de 60 ns ).

Le temps de cycle est l’intervalle de temps minimum séparant deux demandes d’accès successives en lecture ou en écriture

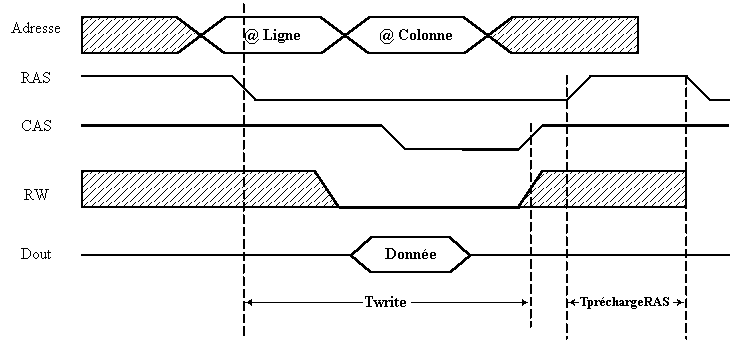

3.3 Cycle d’écriture

3.3 Cycle d’écriture

Le mode le plus fréquent est le mode « contrôlé par CAS ». Le signal d’écriture RW est positionné avant le CAS ce qui provoque l’écriture. Dans le mode ‘late write cycle » on génère le signal RW après le CAS. Dans ce cas c’est le signal RW qui provoque l’écriture. Cela permet de lire et d’écrire un mot en un seul cycle.

- Twrite est la durée du signal RAS en écriture, il est souvent égale à TaccèsRAS.

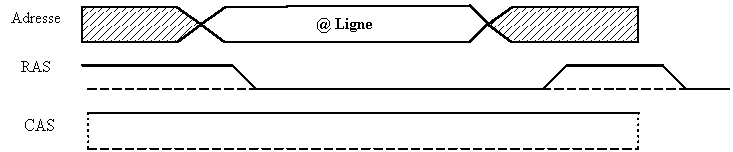

3.4 Cycle de rafraîchissement

A l’intérieur du boîtier, le rafraîchissement se fait par ligne entière. Chaque accès provoque le rafraîchissement de toute la ligne adressée.

Un mécanisme de rafraîchissement doit garantir l’accès périodique à chaque ligne, en fournissant son adresse accompagné du signal RAS. Ceci dit, à ces caractéristiques temporelles s’ajoutent de nombreuses contraintes secondaires comme le temps de pré positionnement des adresses avant le RAS et le CAS, la durée minimale du signal CAS, le temps de pré positionnement de la donnée en écriture avant le RAS etc… Chaque modèle a ses contraintes particulières. Il peut y avoir plus de 40 paramètres temporels…

4- Quels sont les différents types de mémoires ?

4.1 Mémoire FPM DRAM.

Pour de la mémoire DRAM tout court, l’accès à une donnée se fait en modifiant le signal RAS et CAS pour chaque lecture/écriture et ceci même si la donnée suivante se trouve sur la même ligne ou colonne.

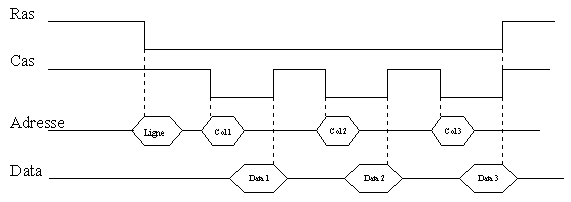

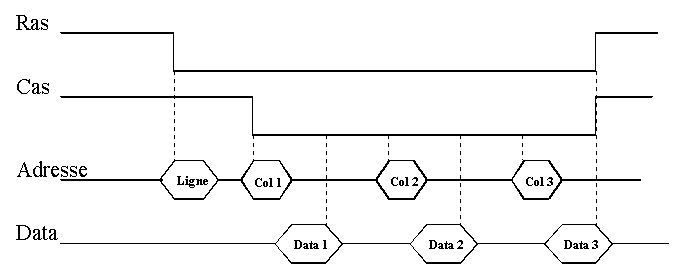

Cycle de lecture de la mémoire FPM

Pour la mémoire FPM DRAM, lorsque la donnée se trouve sur la même ligne, la descente du signal RAS mémorise l’adresse de la ligne durant tout l’accès. Donc pour accéder à plusieurs colonnes de cette ligne ( dans un ordre quelconque ), il est juste nécessaire de présenter l’adresse de la colonne désirée dans la ligne sélectionnée par le RAS. Cela permet d’accélérer l’accès aux données se trouvant sur la même ligne. On économise ainsi le Timing du RAS. Pour accéder à la donnée, le signal CAS doit rester à l’état bas.

La notion de Fast Page vient du fait que la sélection de la ligne correspond à la sélection d’une page dans une livre et la lecture dans cette page correspond à la lecture des différentes colonnes.

Cas de plusieurs accès consécutif :

La mémoire FPM ( Fast Page Mode ) existe en 70 et 60 ns. L’accès le plus rapide de la FPM est 5-3-3-3 ( à 66MHz ) contrairement à la RAM classique qui est de 5-5-5-5. En fait cela correspond au cycle CPU nécessaire à la lecture ou à l’écriture. Cela signifie qu’il faut 5 cycles d’horloge pour lire/écrire la première donnée, puis 3 cycles pour les 3 autres. La bande passante maximale est de 174 Mo/s.

4.2 Mémoire EDO.

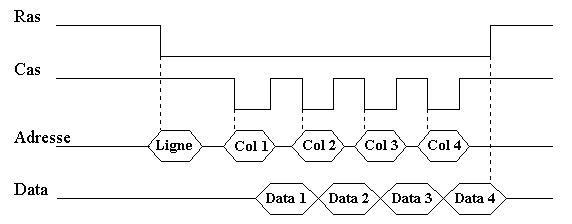

Cette abréviation, signifie Extended Data Out. Les composants de cette mémoire permettent de conserver plus longtemps l’information, on peut donc ainsi espacer les cycles de rafraîchissement. D’autre part, par rapport à la FPM, le signal CAS n’a pas besoin d’être maintenu pour lire la donné, on peut donc anticiper sur le prochain Precharge Time de la mémoire, c’est à dire le prochain cycle mémoire.

La RAM EDO, qui n’existe qu’en modules SIMM, nécessite une logique de rafraîchissement particulière. Elle ne peut donc pas être utilisée sur les anciennes cartes mères de 486 ou de Pentium car les contrôleurs de mémoire de ces cartes ne sont pas conçus à cet effet.

Si le CACHE secondaire constitue le remède le plus courant pour pallier la lenteur de la RAM par rapport à la vitesse des processeurs, la mémoire EDO ( Extended Data Out ou HPM pour Hyper Page Mode) entend parvenir au même résultat ( pour certaines cartes mères non équipées de cache L2 ).

L’ajout d’un verrou de type D (D-Latch) permet de charger une nouvelle adresse en entrée sans attendre la validation d’une donnée en sortie. Les cycles de latence entre deux lectures sont minimisés, d’où un fonctionnement de l’ordre de 50 MHz , contre 25 MHz pour de la DRAM à 70 ns en FPM. Non contente de s’adapter à la fréquence externe d’un processeur comme le Pentium/100, voire le Pentium/133 en mode burst, la mémoire EDO n’engendre qu’un surcoût limité à 5 %. Compatible avec la DRAM classique, elle exige toutefois une carte mère spécifique pour tourner à pleine vitesse.

Cycle de lecture de la mémoire EDO

La RAM EDO permet la réduction de la durée des cycles de mémoire en condensant la temporisation des CAS pour obtenir plus de données en sortie d’une séquence d’accès. En cycle d’horloge cela se représente par 5-2-2-2. Des augmentations de performances des ordinateurs de l’ordre de 15% sont possibles par rapport à la mémoire FPM DRAM. Le débit maximum de la mémoire EDO DRAM se situe aux alentours de 264 Mo/s.

Toutefois, face à la popularité grandissante de la mémoire SDRAM ce type de mémoire devrait débuter son cycle de désuétude vers la fin 1998.

4.3 Mémoire BEDO.

La RAM BEDO (Burst Extended Data Out) est une évolution de la RAM EDO il s’agit d’une variante de l’EDO ou les lectures et les écritures sont effectuées en mode rafale.

Le secret réside dans le mode Burst que l’on arrive à faire supporter à ces composants. On n’adresse plus chaque unité de mémoire individuellement lorsqu’il faut y lire ou y écrire des données. On se contente de transmettre l’adresse de départ du processus de lecture/écriture et la longueur du bloc de données ( Burst ). Ce procédé permet de gagner beaucoup de temps, notamment avec les grands paquets de données tels qu’on en manipule avec les applications modernes.

La RAM BEDO permet d’accélérer les accès en mémoire de 50 % à 100 % pour atteindre 66 MHz. Cela suffit pour obtenir un accès sans Wait States sur tous les systèmes Pentium existant à l’heure actuelle et ceci pour des frais de fabrication à peine plus élevés que pour la classique DRAM.

Comme pour la « simple » RAM EDO, il faut aussi, pour la RAM BEDO, que la carte mère soit adaptée à la technologie en question, c’est-à-dire qu’elle comporte un jeu de puces et un BIOS qui soient capables de supporter ce type de mémoire. La RAM BEDO ne fonctionne pas sur les anciennes cartes mères, pas même sur celles qui comportent un support pour la RAM EDO !

Malheureusement cette mémoire n’était supportée que par peu de chipsets, et posait des problèmes avec les bus cadencés à plus de 66 MHz, d’ou une disparition très rapide du marché. L’accès le plus rapide de la BEDO est 5-1-1-1 à 66MHz.

4.4 Mémoire SDRAM.

La Synchronuous Dynamic Random Access Memory est également une évolution de la classique DRAM. Contrairement à la RAM BEDO, on a choisi ici un procédé très complexe pour accéder plus rapidement aux contenus de la mémoire.

La SDRAM se compose en interne de deux bancs de mémoire et des données peuvent être lues alternativement sur l’un puis sur l’autre de ces bancs grâce à un procédé d’entrelacement spécial. Le protocole d’attente devient donc tout à fait inutile.

La SDRAM peut être cadencée à la même vitesse que le processeur, la deuxième génération de ces composants pouvant atteindre des fréquences jusqu’à 160 MHz. On peut ainsi synchroniser les entrées/sorties avec l’horloge système, ce qui accélère considérablement les échanges. La SDRAM maîtrise en outre le mode Pipelined Burst qui apporte un gain de vitesse supplémentaire, comme pour la RAM BEDO.

La SDRAM n’est disponible qu’en modules DIMM. Il faut donc des emplacements spéciaux sur la carte mère et, comme pour la RAM EDO et BEDO, un jeu de puces et un BIOS adaptés.

C’est la seule RAM actuelle a supporter un bus de 100 MHz ! Enfin du moins théoriquement, c’est ce qui était prévu. En fait les SDRAM 10 ns étaient prévues pour passer à cette fréquence, mais dans la pratique cela ne sera vrai que pour les SDRAM 10 ns de très bonne qualité. Logiquement les SDRAM supportant cette fréquence a coup sur ont des temps d’accès de 8ns …

La vitesse de la SDRAM se mesure normalement en MHz, alors que l’EDO se mesure en ns ( nano seconde ). Si les SDRAM sont spécifiées à 10 ou 12 ns, ces vitesses ne sont pas comparables aux 60ns de l’EDO. Les 10 ns de la SDRAM correspondent seulement à une partie du cycle entrées/sorties mémoire, alors que les 60 ns de l’EDO correspondent à un cycle différent.

Sachez enfin que le changement de mémoire de l’EDO à la SDRAM n’apporte qu’un gain minime sur les performances générales de la machine (1 à 2%).

L’accès le plus rapide de la SDRAM est 5-1-1-1 à 66MHz. Elle est donc synchrone avec l’horloge système pour la lecture/écriture des 3 dernières données. La bande passante maximale est de 524 Mo/s à 66 Mhz et de 800 Mo/s à 100 Mhz.

4.5 Mémoire DDR SDRAM et SLDRAM.

La DDR RAM à 100 Mhz est une autre variante de la mémoire SDRAM. La différence principale entre la SDRAM et la DDR SDRAM est que la DDR SDRAM a la capacité d’utiliser la montée aussi bien que la descente de l’horloge pour transférer les données ce qui a pour conséquence de doubler ses performances de transfert de données. Le taux de transfert maximum de la DDR SDRAM est de 1,6 Go/s .

La SLDRAM est elle cadencée à 200 Mhz.

4.6 Mémoire Rambus DRAM (RDRAM).

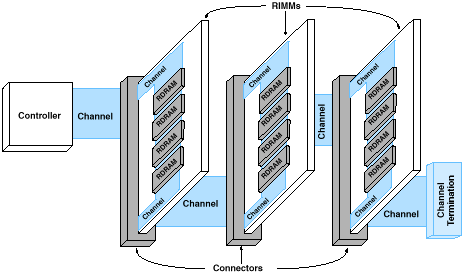

La RDRAM est un concept entièrement nouveau qui utilise une nouvelle architecture de module de mémoire possédant beaucoup moins de broches. Ses principales caractéristiques sont :

une vitesse très élevée de 400 Mhz

une architecture synchrone

l’utilisation de la montée et de la descente des cycles d’horloge ( 800 Mhz pour mes données ).

Puisque chacun des aspects de sa structure interne comme la longueur des conducteurs, les capacité de inter-broche, l’oscillation de la tension ont été rigoureusement redéfinis, ce type de mémoire peut offrir des rendements très élevés. Une simple barrette de mémoire RAMBUS fourni des performances environ de 3 fois supérieure aux modules de mémoire de SDRAM de 64-bits à 100mhz. En fait il s’agit de bloc mémoire de 16 ou 18 bits montés en séries avec une fréquence de 800 Mhz ce qui donne un taux de transfert de 1,6 Go/s.

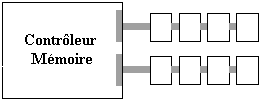

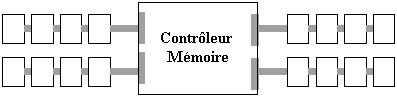

Par exemple un système à un seul canal de cette mémoire peut atteindre jusqu’à 1,6 Go/s de taux de transfert. L’avantage principal avec la Rambus est que des contrôleurs peuvent être conçus pour utiliser 2 ou même 4 canaux en parallèle. Un système à 2 canaux atteindra 3,2 Go/s tandis qu’un système à 4 canaux pourra aller aussi haut que 6,4 Go/s !

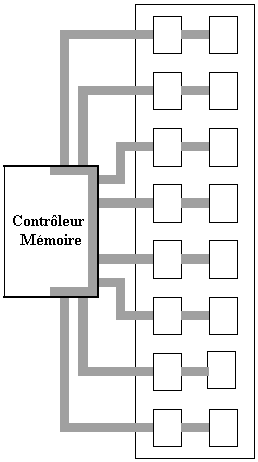

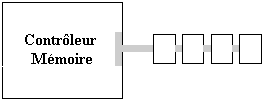

|

Bus mémoire conventionnel |

Bus série RamBus |

|

Fig 1 Il s’agit d’une barette de 64 bits constituée de 16 composants mémoires de 4 bits montées en parrallèles. |

|

|

Contrôleur avec un canal = 1,6 Go/s |

|

|

Fig 2 Il s’agit d’une barette de 64 bits constituée de 4 composants mémoires de 16 bits montées en série. On a donc un bus de 16 bits cadencé à 800 Mhz. ( ( 800 000 000 * 16 ) / 8 bits ) / ( 1024 * 1024 ) = 1,6 Go/s |

|

|

Contrôleur avec deux canaux = 3,2 Go/s |

|

|

Fig 3

|

|

|

Contrôleur avec quatre canaux = 6,4 Go/s |

|

|

Fig 4

|

|

Fig 1

F

Fig 2

Fig 3

Fig 4

Les barrettes RDRAM peuvent être chaînés sur une bus.

4.7 Mémoire Auto-correctrice ECC et AECC.

La mémoire ECC ( Error Correcting Code ) est une mémoire qui peut détecter 4 erreurs et corriger une erreur sans arrêter le système.

Alors que la mémoire AECC ( Advanced Error Correcting Code ) est une mémoire qui peut détecter 4 erreurs et corriger 4 erreurs sans arrêter le système.

On à donc une augmentation du niveau de sécurité, la contre partie de ce gain de sécurité est une consommation plus importante des ressources système pour enregistrer les données. Ce qui dégrade légèrement les performances du système.